请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS62A04AB 工具/软件:

您好、

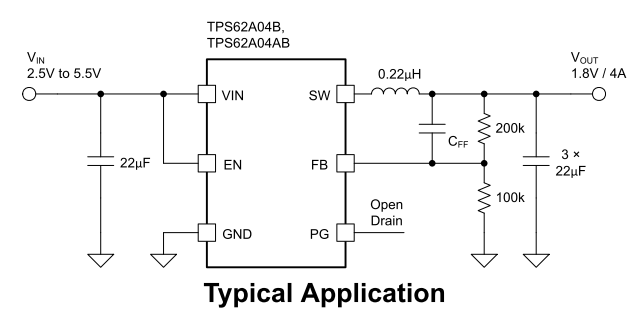

您能否帮助评估仿真的可行性:使用 TPS62A04BDRLR (规格中所示的电路配置)、输入/输出为3.3V/0.825V、并根据连接的电流曲线、仿真在1MHz 的条件下、Vout 纹波是否可以在±1.5%以内?

- 电流曲线:E 列-时隙单位=秒、F 列- 128位 VDDAC 单位= A。请仿真该列中电流变化下的 Vout 纹波。

- 我是否需要提供电感器(L)和电容器(C)的实际器件型号?

- 电容器的数量是否可以进一步优化? 如果 Cout = 22uF*2、结果是什么?

- 如果当前配置文件持续时间过短、您可以将 F 列(128位 VDDAC)中与 E 列中的时隙相对应的当前值从3.00E-08复制到4.00E-08、并将它们附加到 F 列中当前值的末尾以进行扩展。

e2e.ti.com/.../DQ_2B00_CA_5F00_wrl_5F00_VDDAC_5F00_current_5F00_profile.xlsx

谢谢