工具/软件:

尊敬的专家:

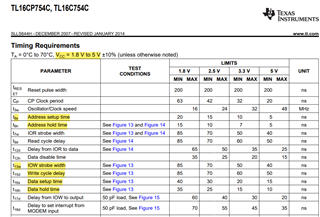

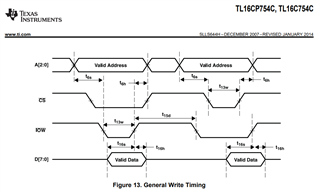

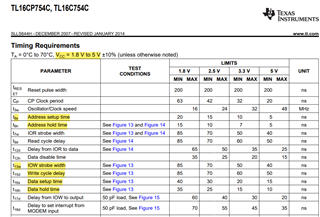

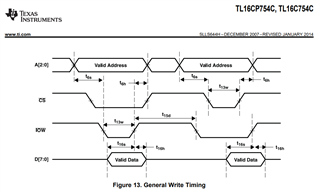

客户发现他们可以读取寄存器、但无法成功写入寄存器。 现在、他们测试时序 t6s、t6h、t13w、t16s 都高于1us。 那么、您能否给出一个基于逻辑分析波形的写入命令示例? 它将是客户的参考。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家:

客户发现他们可以读取寄存器、但无法成功写入寄存器。 现在、他们测试时序 t6s、t6h、t13w、t16s 都高于1us。 那么、您能否给出一个基于逻辑分析波形的写入命令示例? 它将是客户的参考。

尊敬的 Clem:

在写入命令之前添加复位选项、写入成功。 您是否有 TL16C754C 的编程文件或用户指南?

此器件设计为与原始 IBM PC 中的8250 UART 兼容、并可与16550等更高版本的扩展兼容。

en.wikibooks.org/wiki/Serial_Programming UART/8250_UART_Programming

intel.com/content/www/us/en/docs/programmable/683130/22-2/16550-uart-general-programming-flow-chart.html