工具/软件:

您好、

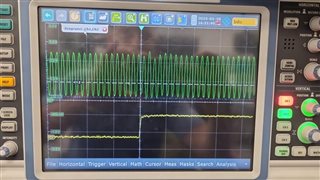

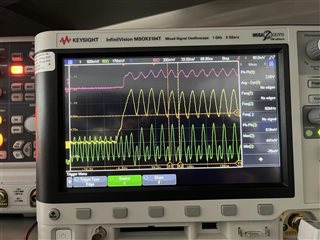

我们已将 EVM 连接为仅接收、并对 RXD/CLK/ER/DV 信号(2GB、100Mhz 并行- GTX_CLK)上的数据进行采样。

器件正在同步(RX_DV/ER 置为无效)、我们将使用 FPGA 板(基于 MPSoC)对并行数据进行采样。

我们可以观察到、在传输'hffff 数据等之后、整个16位字在特定位置存在采样不匹配情况。

所有数据重置似乎都正确。 未检测到同步松散且未检测到 ER 置为无效。

请协助找出可能是什么原因?

我们怀疑电路板一旦拉动更大的电流、会出现弱 RX_CLK。 一旦我们收到这些罪魁祸首的话、我们就会看到它正在改变"形状"。

谢谢

Doron