请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83822I 工具/软件:

您好:

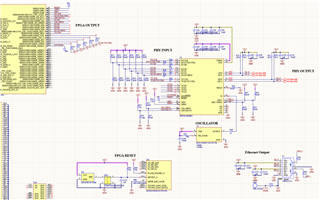

我在让 DP83822IRHBT 与 FPGA 配合使用时遇到问题。 它导通、消耗电流、未处于复位或 PWDN 状态、我已多次检查搭接引脚。 我移除了 LED 串联电阻引脚、因为我最初没有上拉和下拉电阻。 我不知道为什么我会从 TX CLK 和 RX CLK 获得平坦的0V 电压。 有什么想法吗?

谢谢您、

Blake