工具/软件:

您好团队:

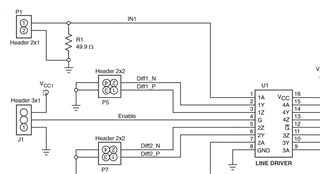

在 SN65LVDS31-32EVM 中、驱动器输入端放置了一个 49.9Ω 电阻器、该电阻器与 FPGA IO 引脚 (XC7S50-1FGGA484C) 连接。 在给定 3.3V 信号电平时、该电阻器可以允许高达约 66mA 的电流流动 (I = 3.3V / 49.9Ω≈66mA)。

然而、FPGA IO 引脚仅支持大约 25mA 的最大电流、因此这会带来超过 FPGA 引脚电流额定值的潜在问题。

您能否澄清一下 49.9Ω 电阻器是否应按原样使用、或者是否建议使用值更高的电阻器来确保 FPGA 引脚电流保持在安全限制范围内? 此外、有关将 FPGA IO 与 SN65LVDS31-32EVM 驱动器输入连接的最佳实践的任何指导都将非常有用。

提前感谢。