工具/软件:

您好、

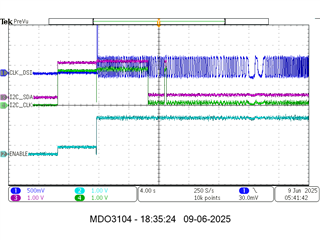

我们面临着一个类似的问题、即我们使用 DSI83-Q1 进行 MIPI 至 LVDS 转换。 我们使用 DSI REFCLK 作为参考时钟。 连接的波形为启动序列。

我们看到、有时屏幕会随机出现空白。

我们正在尝试在实验中重现该问题、我们认为应通过短接抖动来将抖动随机引入 DSI CLK。 我们看到的是,在短时间内,有时屏幕自动恢复,而有时它根本不会恢复。 我们已验证同步时间、DSI 和 LVDS 同步时间相同、并且在启动中没有发现问题。

我们希望详细了解这一点-

1.为避免 PLL 解锁、可以采取哪些措施来避免此类问题(均衡,LVDS 端接)等。

2.为什么问题会自动恢复,而不是其他时间 — 可以调整什么(如果有 PLL 锁定时间等限制)使其自动恢复?