Thread 中讨论的其他器件: DP83825EVM

工具/软件:

TI 团队大家好、

这是我前面关于电源斜升期间 DP83825I REF_CLK 的问题的跟进信息: https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1486923/dp83825i-clock-availability-at-power-ramp/5715771#5715771

我们已根据您的建议更新了我们的设计、现在会在 REF_CLK 稳定后将复位置为有效。 但是、在这种变化之后、我们注意到以下行为:

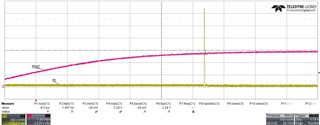

- 复位取消置位后、我们会在 RX_ER/DV 引脚上观察到单个尖峰/干扰(请参阅随附的示波器屏幕截图)。

- RX_ER/DV 用作自举引脚、具有 数据表中建议的 2.49kΩ 下拉电阻。

- 在出现干扰后、RX_ER 保持低电平、PHY 似乎可以正确引导。

- RESET 和 REF_CLK 斜升看起来正确、并且尖峰仅显示一次。

在 RESET 上升后出现干扰。

我的问题:

- 这是否是 RX_ER 在复位置为无效后显示干扰的已知问题?

- 这种干扰是否会影响自举采样、或者只要在复位上升时 RX_ER 处于低电平、它是否安全?

提前感谢您的支持!

此致、

Hamza.