请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TUSB1210工具/软件:

你(们)好

我目前正在设计中使用 TUSB1210BRHBR。

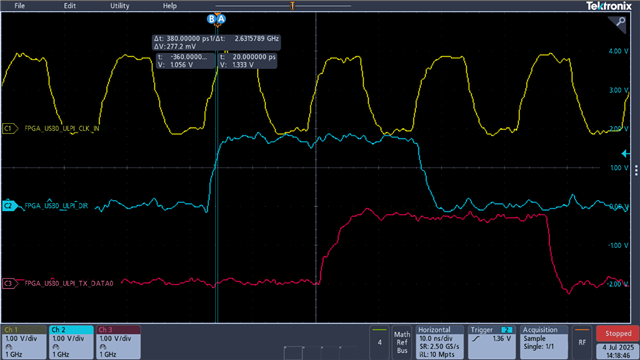

我测量了 NXT 和 DIR 的输出延迟、两者始终低于 1.2ns。

以下是我的测试环境的详细信息:

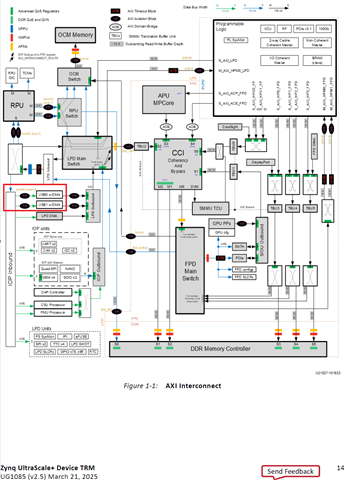

FPGA:XCAU7P-L1SBVC484I

示波器: 3 系列 MDO 混合域

探头: TPP1000

时钟为 输出模式。

TUSB1210BRHBR 的数据表规定输出延迟范围为 1.2ns 至 5.5ns。

根据 ULPI 1.1 规范、延迟应小于 9.0ns。

即使符合 ULPI 规范、在数据表规格之外运行是否存在任何潜在风险或问题?

谢谢、此致

Chunli Liang