工具/软件:

您好:

我想问一个有关以太网 PHY 用例的一般问题。

通常、台式计算机在不拔下 LAN 电缆的情况下关闭。 (链路伙伴:路由器/交换集线器已通电、但使用 PHY 的计算机本身已断电。)

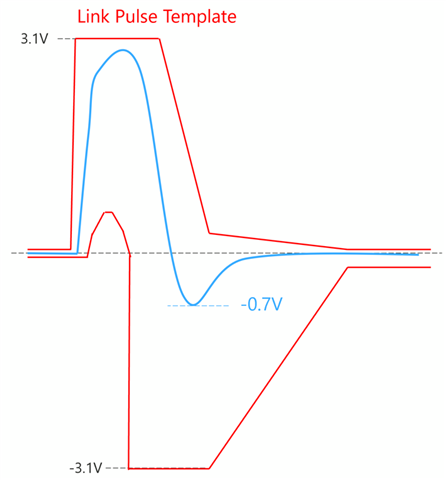

在这种情况下、该计算机中的以太网 PHY 会持续接收 NLP/FLP、这些信号可能会出现下冲低于数据表中所述的绝对最大额定值。

下冲可能取决于电路板设计、但我可以在 E2E 中找到一些超过–0.5V 的波形。

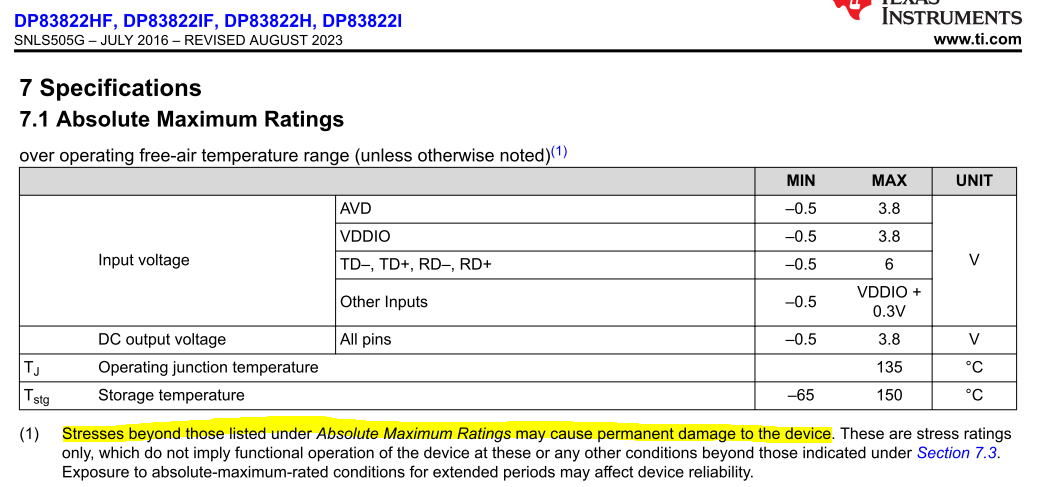

由于器件接收的电压超过绝对最大额定值、因此我认为器件可能会损坏。

TI 器件是否能够承受此类用例?

对于 MDI 引脚、大多数器件似乎具有–0.3V 或–0.5V 的绝对最大额定值最小值。

是否不建议在系统 (PHY) 通电之前连接 LAN 电缆?

此致、

Kawai