工具/软件:

你(们)好

我在我设计的电路板上使用了一个 PHY [DP83867IRRGZT ]、但在关断序列检查期间、它的行为与预期不同、违反了 FPGA 关断序列、因此我正在寻找一种方法来改进这一点。

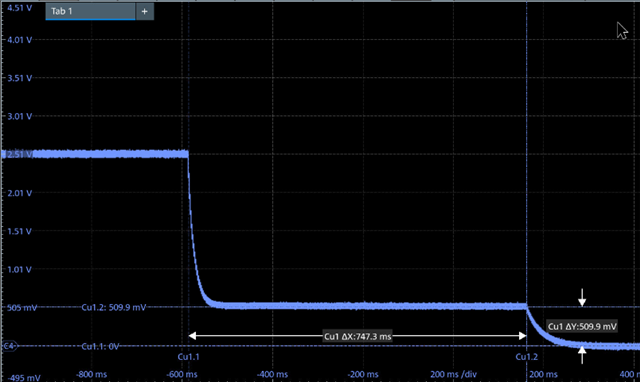

在为系统上电并建立以太网通信后、在关闭系统电源时、提供给 PHY 的 2.5V 电压保持在 500mV 左右 750ms、然后在 100ms 内放电至 0mV。

如果未建立以太网通信、则电压不会保持在 500mV、并立即放电至 0mV。

PHY 采用双电源配置 (1.0V、2.5V) 和 1.8V VDDIO 电源运行。

模式设计如下:

RX_D0:PHY_ADDEN、1⇒MODE1

RX_D1:PHY_ADD2、3⇒MODE1

RX_CTRL:AutoNeg⇒MODE3

LED_2:RGMII 时钟偏移 Tx[0]、[1]⇒MODE1

LED_1:ANEG_SEL、RGMII 时钟偏差 Tx[2]⇒MODE1

LED_0:MirrorEnable⇒MODE1

GPIO_0:RGMII 时钟偏斜[0]⇒MODE1

GPIO_1:RGMII 时钟偏斜[1、2]⇒MODE1

我将发布捕获的波形。

这是否是 PHY 的特性?

或者、是否可以通过调整 OHR 设置来解决该问题?

请告诉我。

最好的评价、Kato