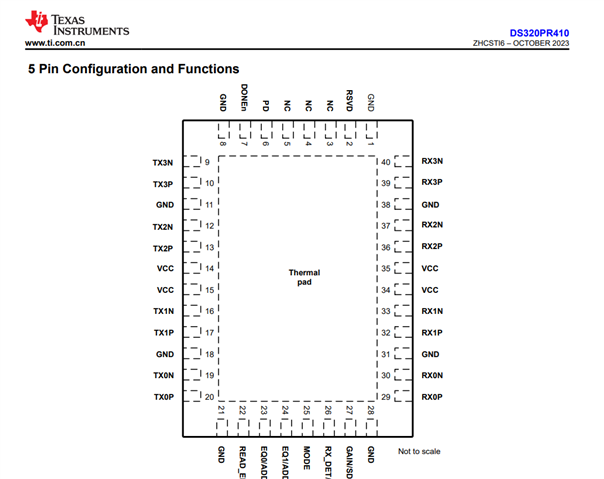

Other Parts Discussed in Thread: DS250DF230EVM, DS250DF230, DS320PR410

主题: DS250DF230、 DS320PR410 中讨论的其他器件

工具/软件:

您好、

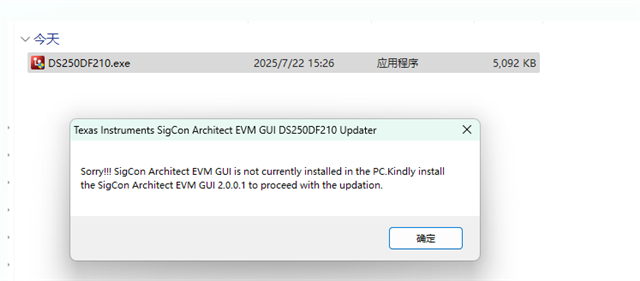

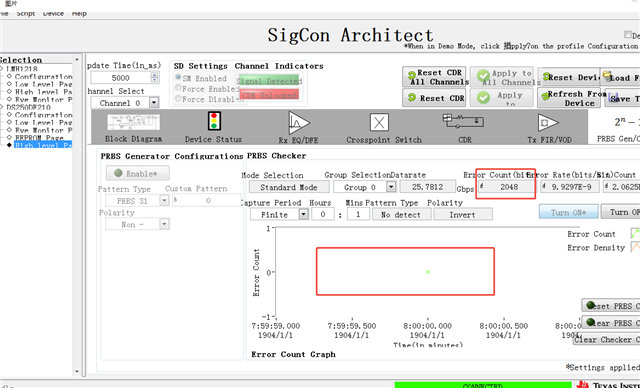

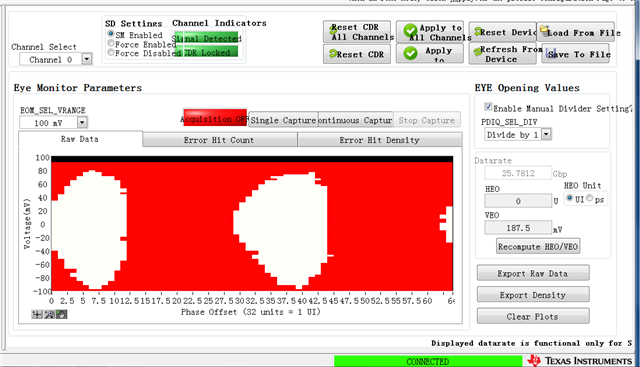

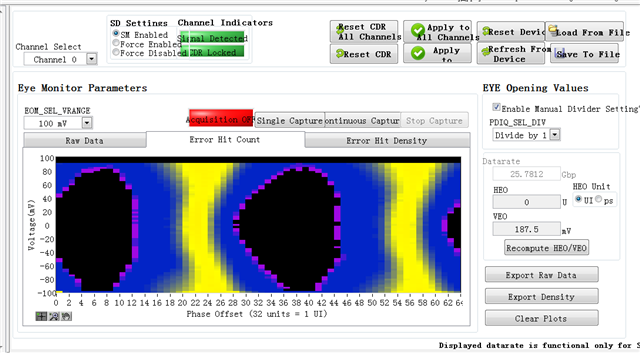

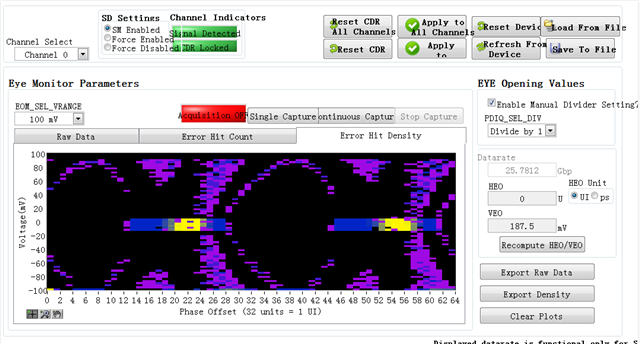

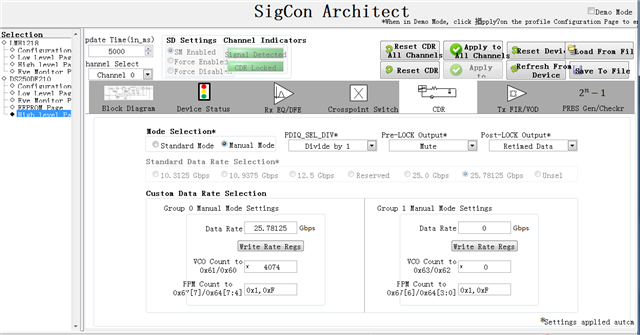

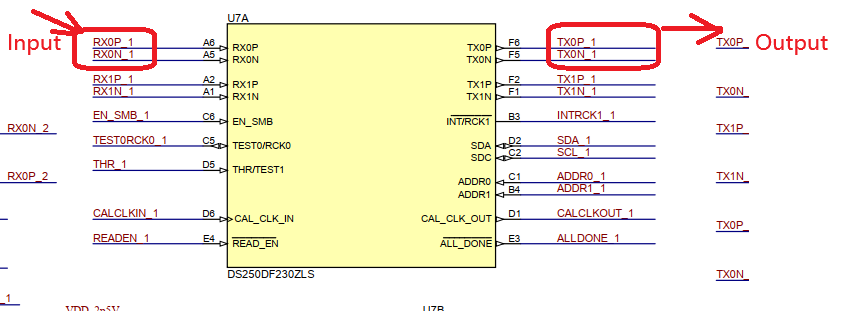

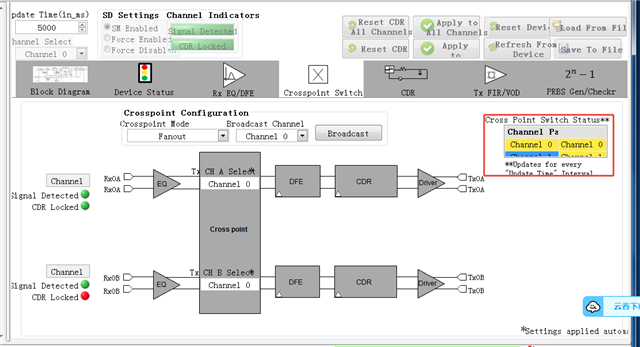

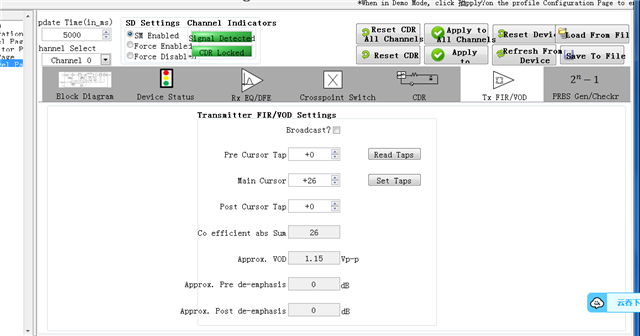

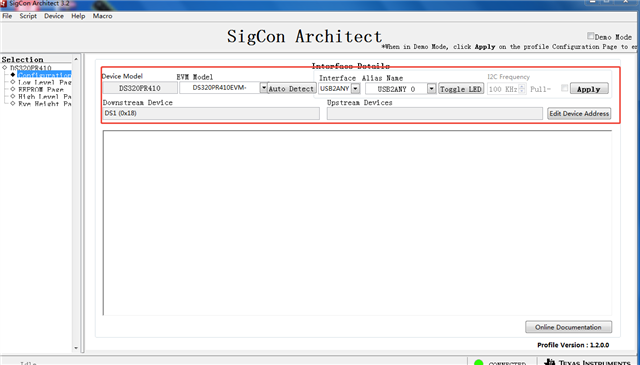

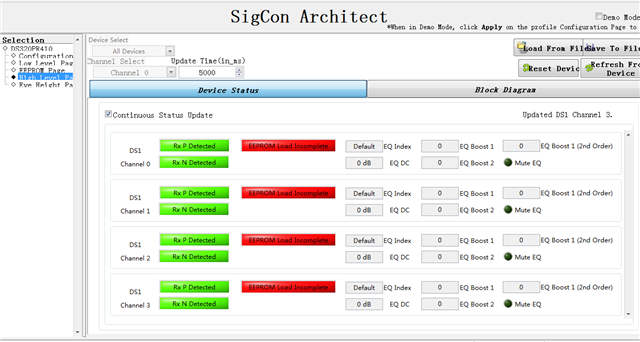

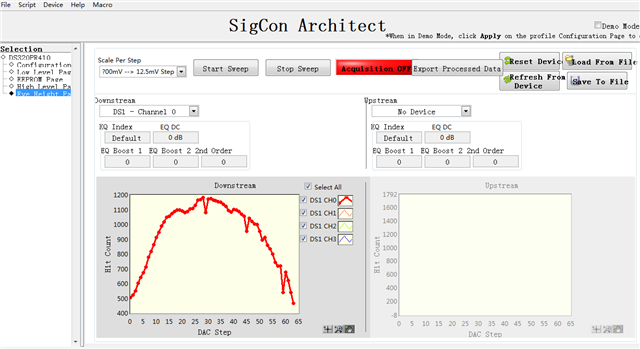

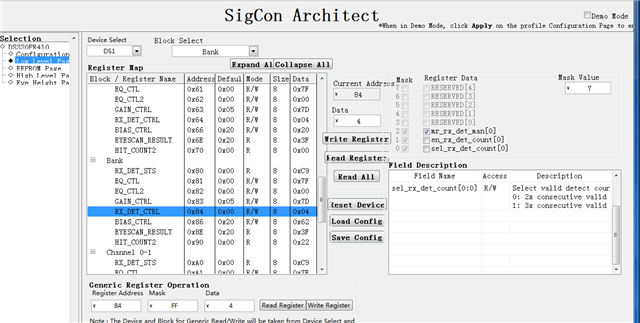

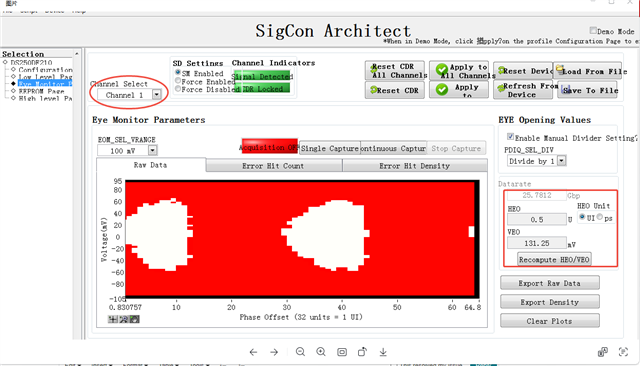

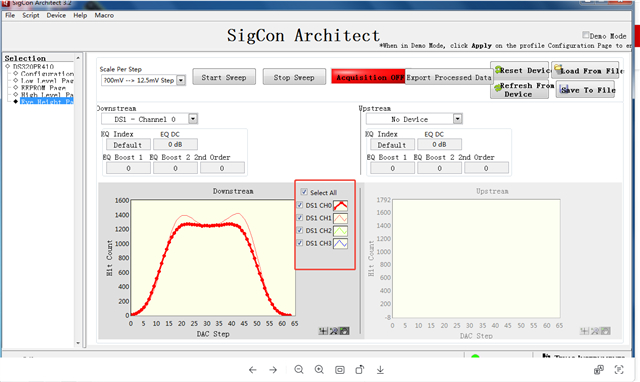

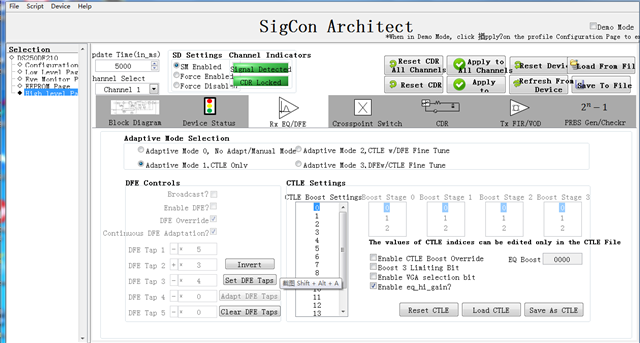

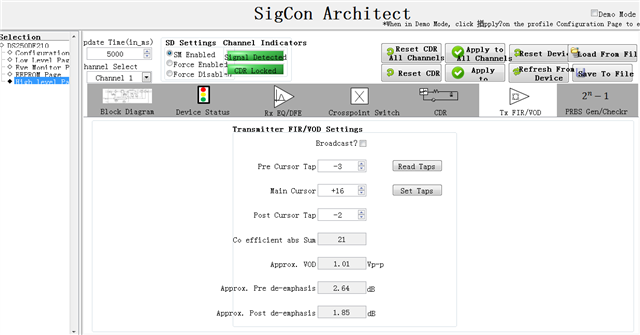

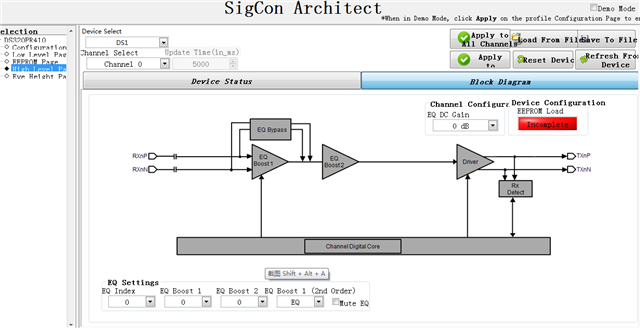

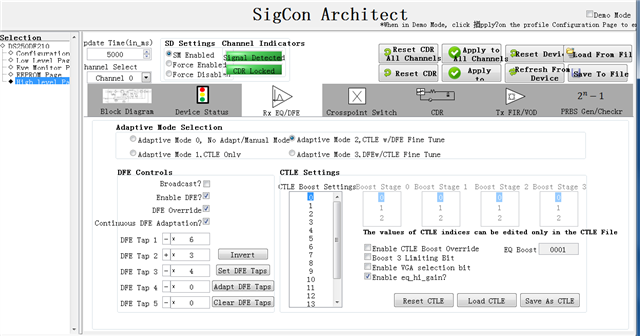

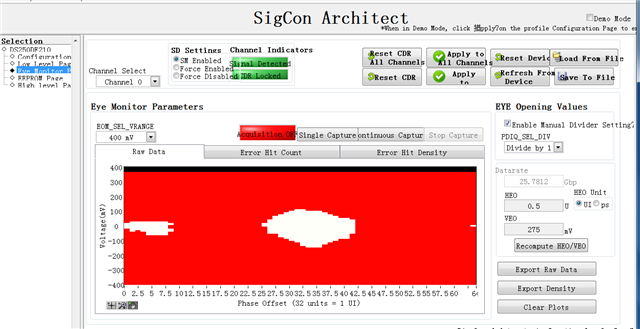

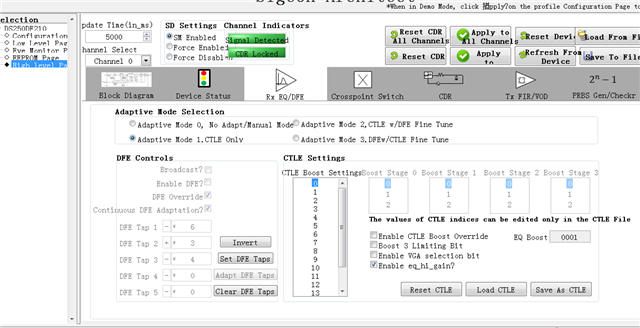

我想使用 DS250DF230EVM、下载 DS250DF230 器件配置文件并安装此程序后、它包含如下图所示的信息。

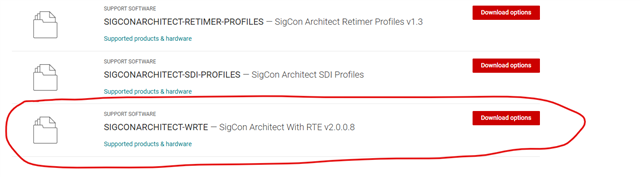

此器件配置文件需要 SigCon Architecture EVM GUI 2.0.0.1、但 TI 网站中较早的软件是 2.0.0.8、如何使用该软件?

非常感谢。