主题中讨论的其他器件: SN65LVDS31

工具/软件:

大家好、我正在使用 SN65LVDS32 进行处理 CAT5 数据信号的设计。 根据我的当前原理图、当 没有信号 发送到 CAT5 输入插孔时、引脚将保持不可预测状态。

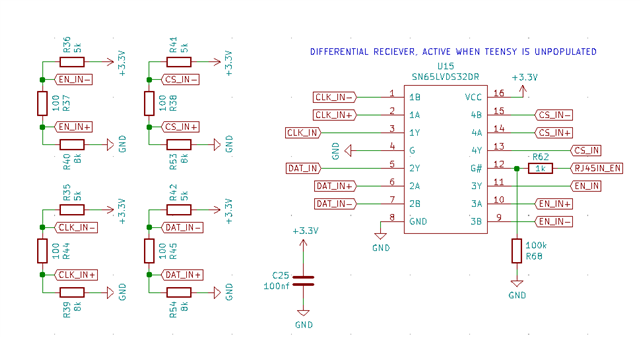

这是我的电流原理图、在差分输入端有一个 100 Ω 的迟滞电阻器、并且正极和负极信号都通过 10k 电阻器偏置到地:

我发现、对于来自 SN65LVDS31 的 CAT5 信号、此原理图适合我。

但当未插入任何器件时、某些输出为高电平、而某些输出为低电平、看似随机。

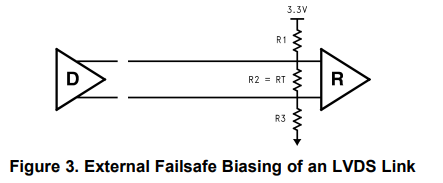

当没有接收到差分信号时 、所有输出都需要变为低电平。 要完成此操作、我需要进行哪些更改?

请提供建议。