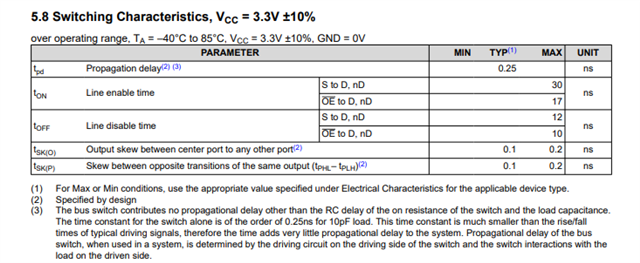

Other Parts Discussed in Thread: TS3USB221A

工具/软件:

尊敬的 TI 团队:

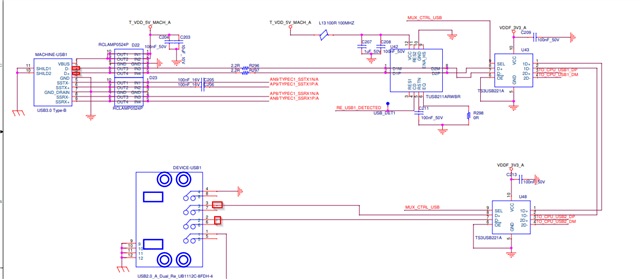

我在使用 两个 TS3USB221A 用于构建 USB 多路复用器/“小环路“电路的芯片。

目标/预期行为

-

何时 MUX_CTRL_USB =高电平 :两个 USB 端口 (PC_USB 和 DEVICE_USB) 都应连接到 CPU (RK3588)。

-

何时 MUX_CTRL_USB =低电平 :两个外部 USB 端口应短接在一起 TS3USB221A 进行通信 运行起来就像一个简单的设备 USB 中继器/桥接器 (PC 侧

器件侧) 、绕过 CPU。

实际结果

-

何时 MUX_CTRL_USB =高电平 (端口→CPU):两个端口都正常工作。

-

何时 MUX_CTRL_USB =低电平 (中继器模式): PC 已连接到 PC_USB 无法枚举 鼠标/键盘连接到 DEVICE_USB 。 PC 显示没有新设备。

设计总结

-

×Ω TS3USB221A(高速 USB 2.0 模拟开关)、每个开关处理 D+/D−。

-

CPU 侧:RK3588 USB OTG(高速)。

-

外部端口:

-

PC_USB →连接到主机 PC。

-

Device_USB →连接到 USB 设备(鼠标/键盘)。

-

-

每个端口上的 VBUS 都会进行路由(PC_USB 上的 PC 提供 5V 电压;需要时为 DEVICE_USB 提供 5V 电压)。

-

连接器上的 ESD 保护;控制器附近的 22Ω 串联电阻器;D+/D−的受控阻抗布线。

症状/观察

-

通过快速切换到中继器模式、 主机 PC 不检测任何低速/全速器件。

-

如果我将器件直接连接到 PC(无中继器)、它会正常进行枚举。

问题

-

通过 TS3USB221A “短接“两个 USB 连接器是否有效 (即使用开关将主机端口的 D+和 D−直接连接到器件端口)、或者 USB 是否需要 有源中继器/ HUB/PHY 该用例中的 CMRR 性能?

-

指定 USB 角色检测(DP/DM 上拉/下拉和 VBUS 存在) 、在使用 TS3USB221A 切换路径时、是否需要额外的组件或时序控制?

-

我需要吗 栅极或延迟 VBUS 或 DP 1.5kΩ 上拉 以便主机可以重新检测连接?

-

-

都有 推荐的应用手册 如中所示使用 TS3USB221A 主机

器件桥接 场景(不仅是主机/器件

CPU 多路复用器)?

-

我需要吗 击穿风险 在断开 CPU 与建立 PC

器件路径之间、为了避免部分连接?

-

不限 速度限制 (LS/LS/HS/HS FS) 或 信号完整性限制 当像这样背对背级联两个 TS3USB221A 器件时?

-

TI 会建议吗 不同的器件(例如 USB 集线器、转接驱动器或专用 OTG 开关) 实现可靠的“PC

USB 设备“直通?

附件(待添加)

-

原理图 PDF:TS3USB221A_MUX_Snippet.pdf

非常感谢您对我的方法是否有效以及需要哪些更改(上拉/下拉、VBUS 控制,时序或其他器件)的指导。

此致、

Wang