主题中讨论的其他器件:AM6442、 DP83869、 TMDS64EVM

工具/软件:

您好、

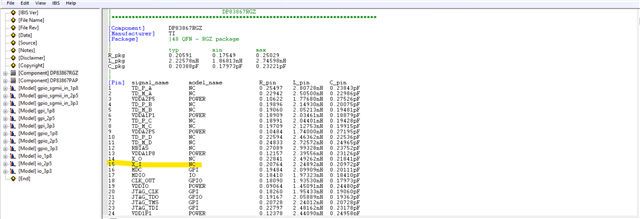

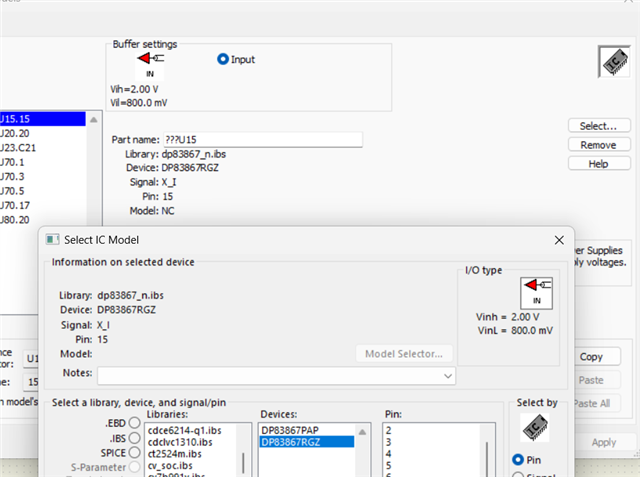

在 DP83867IRRGZT 的 IBIS 模型中、引脚 15 (X_I) 标记为 NC 、但仿真向导将 VIH 显示为 2V、VIL 显示为 800mV、 这与 我使用的 1.8V 逻辑电平不匹配。 AM6442 处理器也会出现同样的问题、其中引脚 C21 在 IBIS 模型中也标记为 NC。 我使用了您网站上的最新 IBIS 模型、更改 Vih/Vil 值似乎会影响仿真中的下冲/过冲。 您能澄清一下吗? 我将提供快照供您参考。