Other Parts Discussed in Thread: CSD87502Q2, TIDA-01238

主题中讨论的其他器件: TIDA-01238

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: CSD87502Q2, TIDA-01238

您好、Emma、

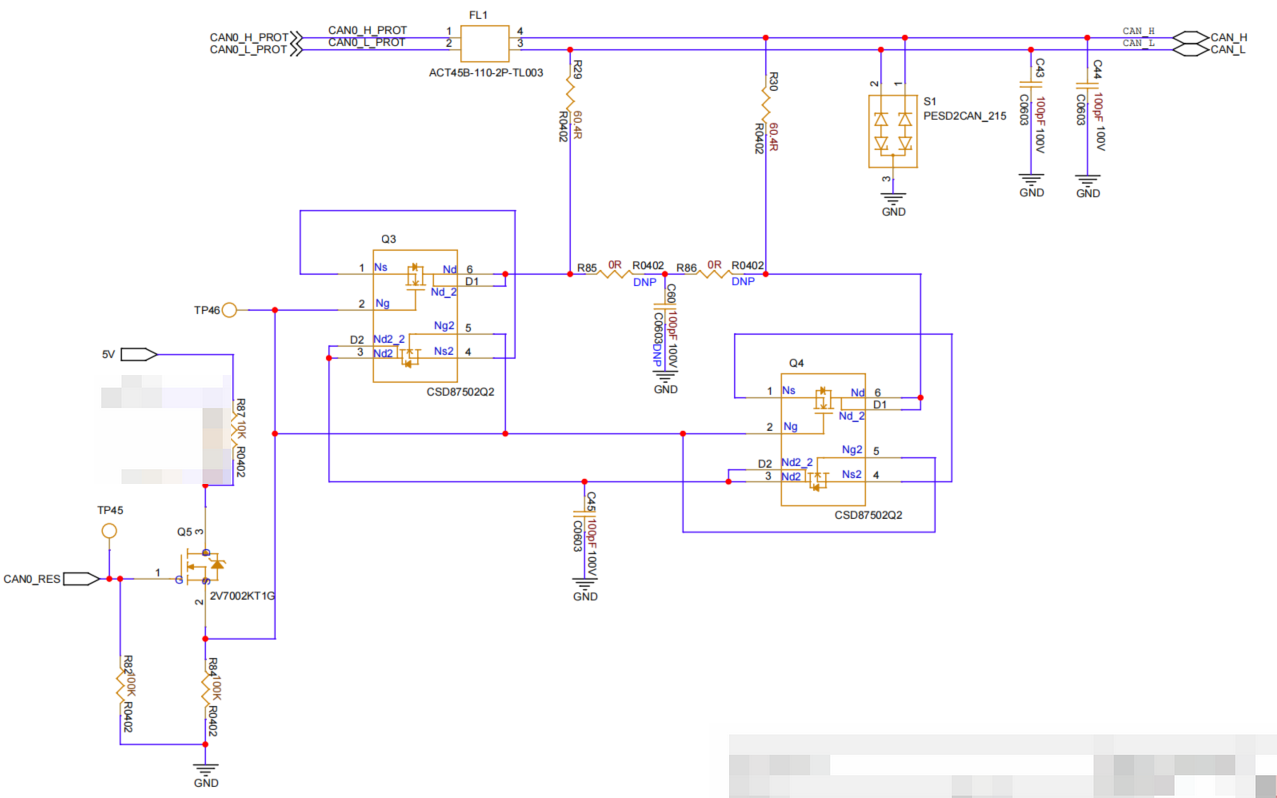

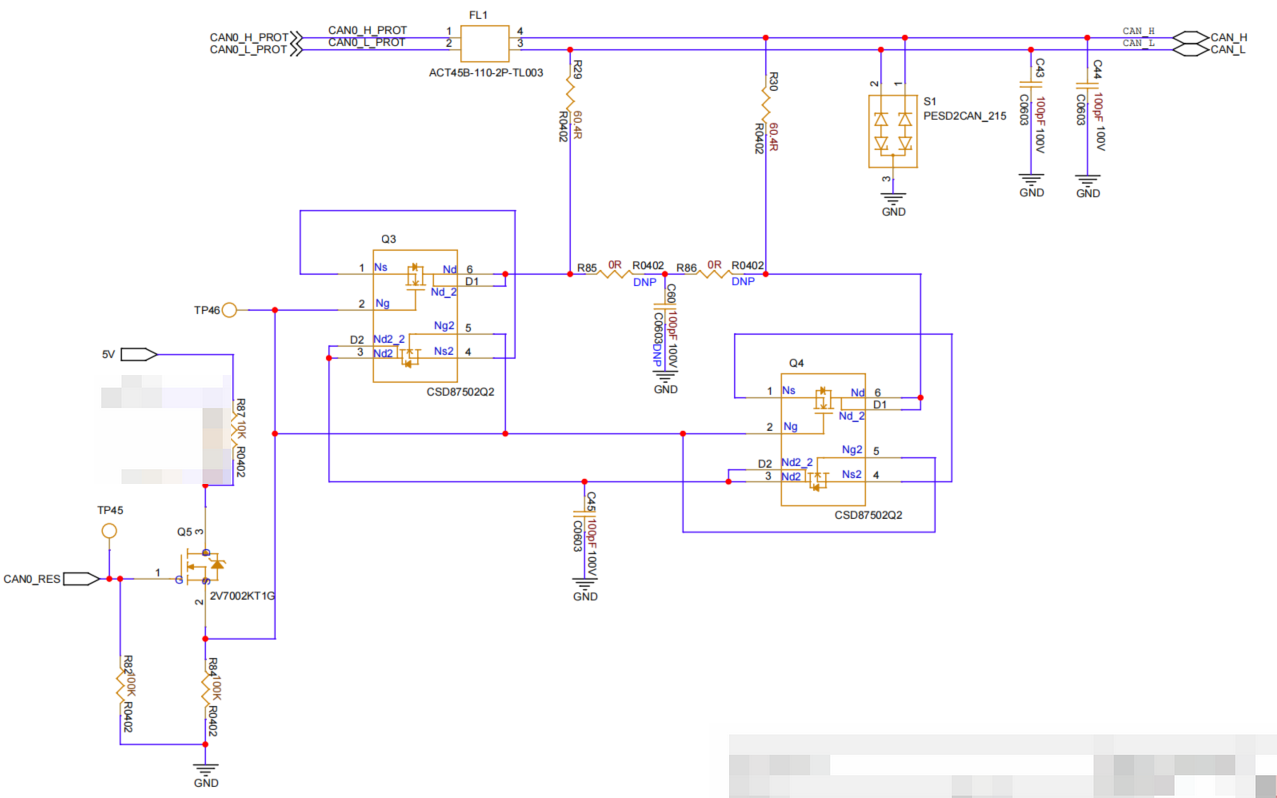

感谢您关注 TI FET。 我不熟悉这种类型的应用。 从原理图中、我可以看到所有栅极都连接在一起、并由 Q5 的源极驱动。 当 Q5 开启时、Vgate = 5V x (R84/(R84+R87))= 5V x (100K/(10K+100k))= 4.55V。 我还看到 Q3 的源极连接在一起、Q4 的源极连接在一起。 但是、Q3 和 Q4 的源极端子悬空、不以 GND 或其他电压为基准。 什么是 VGS? 您能提供 VGS 波形吗? 为了使 FET 导通、VGS ≥3.8V、数据表中指定了 RDS (on) 的最小值。 CAN_L 和 CAN_H 的预期波形是什么? 它们应该是方波吗? 我期待您的答复。

此致、

约翰·华莱士

TI FET 应用

您好 John Wallace:

我们的设计参考了贵公司的相同 MOS 开关电路、但我们这边的测试波形与贵公司的测试波形不同。 您能帮助咨询并确认这一点吗?

您好、Emma:

测量 4.5V GATE 与 GND 可能不够。 即、如果 FET 的源极节点在某个中间 CAN 电压下悬空、则实际 VGS 可能太小而无法导通。 因此、在隔离/分离的情况下测量时、它似乎导通、但在使用 CAN 进行连接/测量时不导通。 我怀疑这是 CAN 节点 CAN 共模电压通常处于 1/2 VCC 或 2.5V 隐性状态造成的。

您可能会注意到栅极电压变为 4.5V、但源极电压接近 1/2 VCC、这意味着 VGS 接近 2V 是最可能的根本原因、并建议通过移除/更改分压器网络来更改栅极驱动、以在预期范围内产生 VGS、从而让获取完整的 5V 电压、并确保源极低到足以产生所需的 VGS。 如果不可行、还可以考虑在较低 VGS 规格下具有较低 Rdson 的 FET。

此致、

Michael。