Other Parts Discussed in Thread: SN65DSI84-Q1, SN65DSI84, SN65DSI83

器件型号: SN65DSI84

主题中讨论的其他器件:、 SN65DSI83

您好 TI 支持团队:

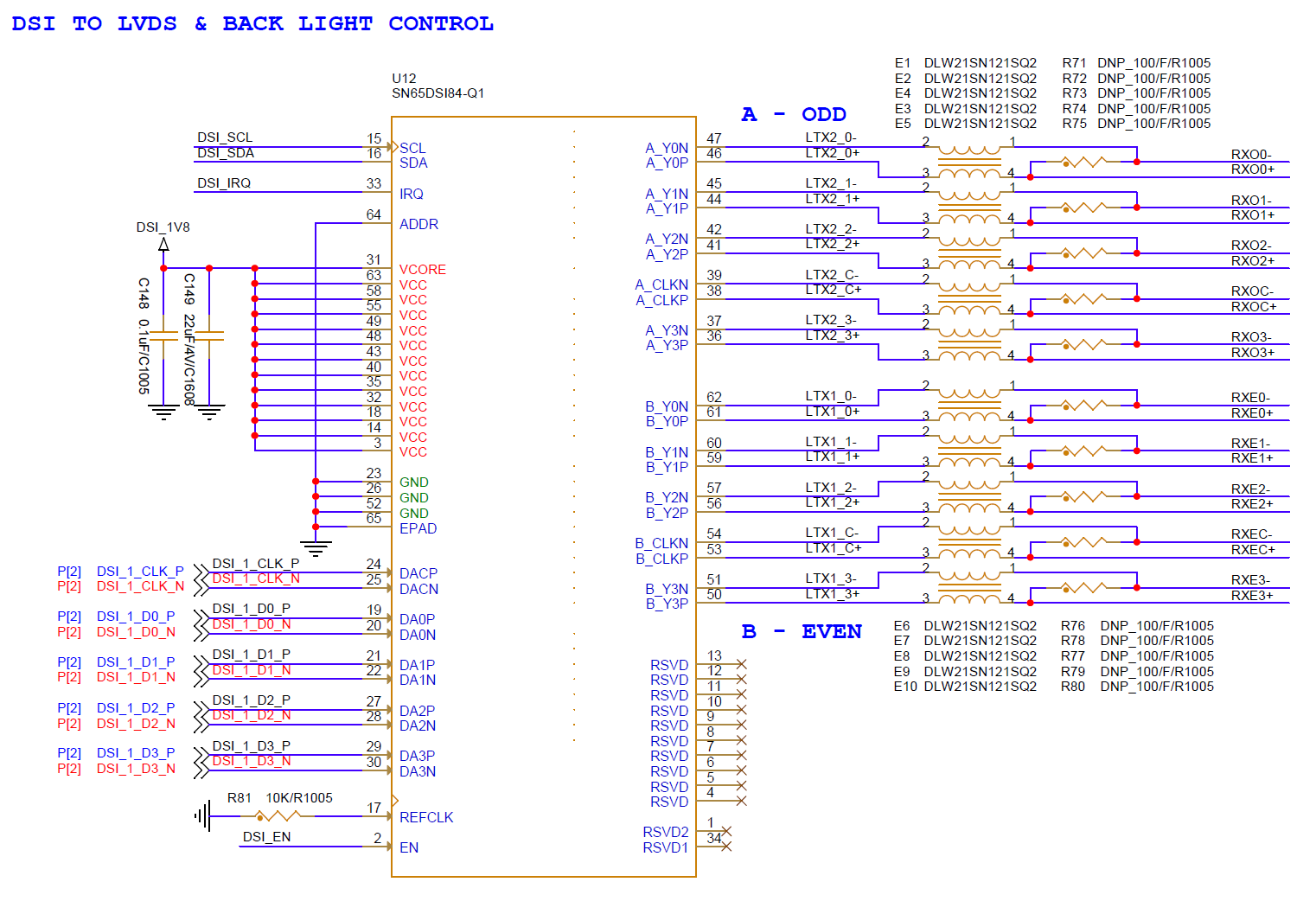

我们使用的是 Raspberry Pi 计算模块 4S (CM4S) 和 SN65DSI84-Q1 将 DSI 转换为 双路 LVDS LCD 面板的 GPIO 输出。

我们希望生成正确的结果 使用 SN65DSI8x DSI 调谐器工具时的寄存器设置 、但我们不确定根据我们的面板规格在工具中输入的确切时间值。

以下是面板数据表中的时序信息(仅降压模式,60Hz):

| 参数 | 符号 | 典型值 | 人员 |

|---|---|---|---|

| 水平活动 | Tdisp (h) | 960 | Tclks |

| 水平消隐 | Tblk(h) | 322. | Tclks |

| 垂直活动 | Tdisp (v) | 540 | TH |

| 垂直消隐 | Tblk (v) | 45 | TH |

| 像素时钟 | Fclk | 45 | MHz |

| 帧频率 | FV. | 60 | Hz |

| 水平频率 | Fh | 35.1. | KHz |

我们的配置:

-

输入: 来自 Raspberry Pi CM4S 的 DSI

-

输出: 双 LVDS(A/B 通道激活)

-

REFCLK: 已连接但无外部时钟源(使用 DSI 时钟输入)

请确认:

-

事件 值应输入到 DSI 调谐器工具中 (用于像素时钟,水平/垂直活动、消隐、同步宽度、前沿/后沿、 等)进行编程?

-

不限 示例配置 或 参考工程 接近这个时间?

非常感谢您的指导和支持。

此致、