德拉斯,

我是MarubunArrowe2e.ti.com/.../7268.DSI83_2D00_Q1-problem.xlsx的FAE

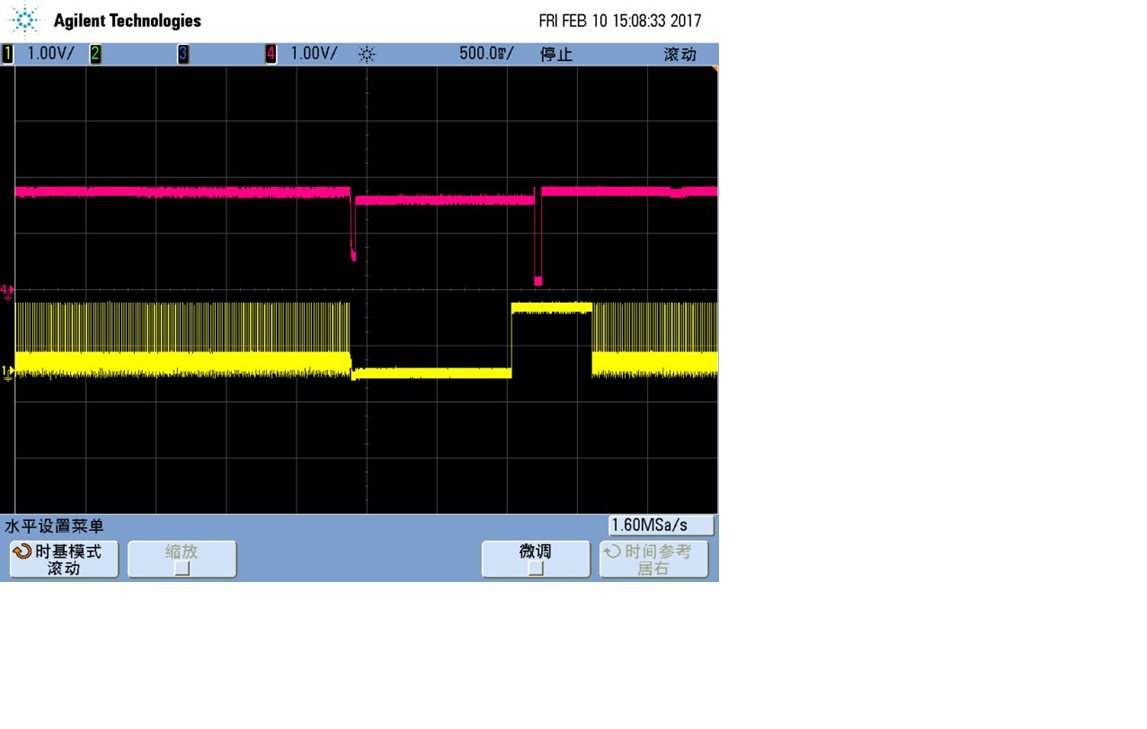

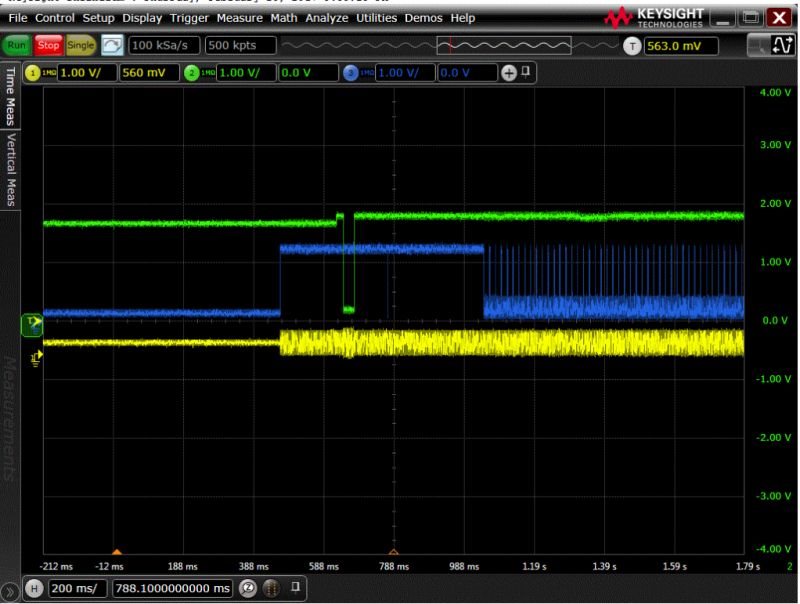

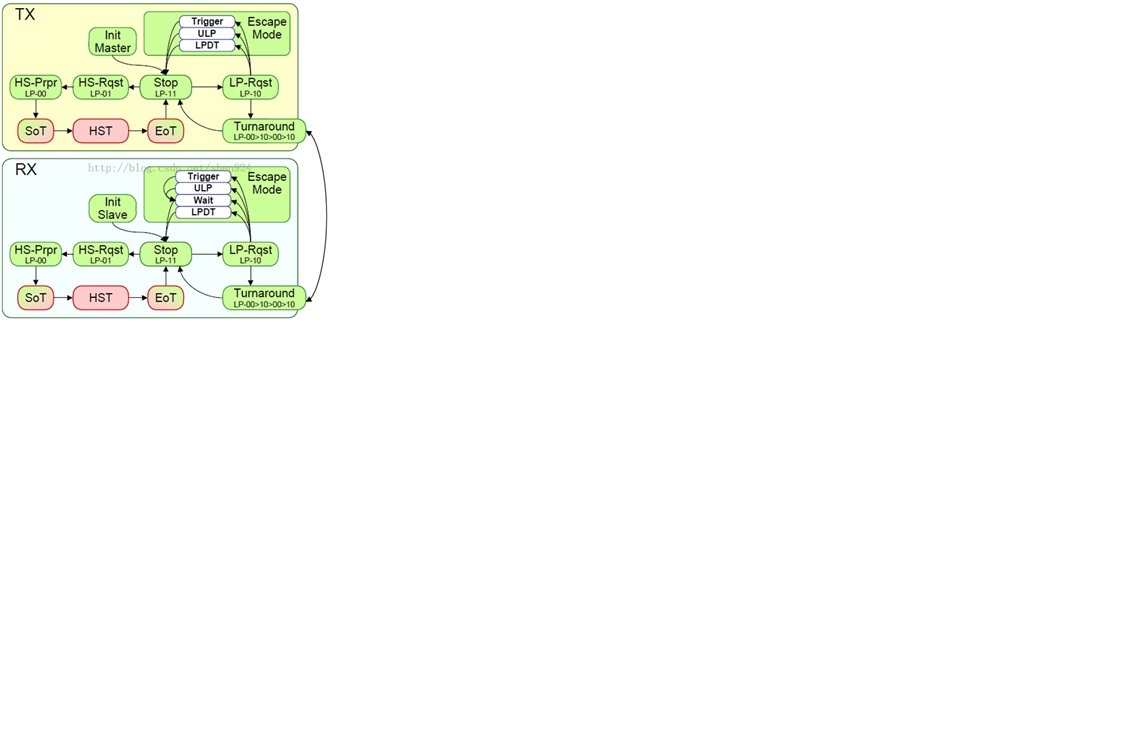

我的客户使用SN65DSI83-Q1将MIPI转换为LVDS (LCD显示屏),现在它可以使用测试模式显示,但不能使用DSI输入显示。0xE5寄存器数据为0x09。

我们检查初始顺序, 它是否符合数据表,我们还检查DSI输入时钟,它是否正常。

我们的客户在同一主板中使用其他供应商的IC,它可以正确显示。

包含波形,设置和寄存器数据。

我想知道哪个问题会导致错误:0x09,以及如何解决? 请提供您的建议---谢谢