您好,先生:

很抱歉打扰你。

作为标题,我们使用 SN65DSI84并下载工具“sllc434c.zip”

我们有一些问题需要检查

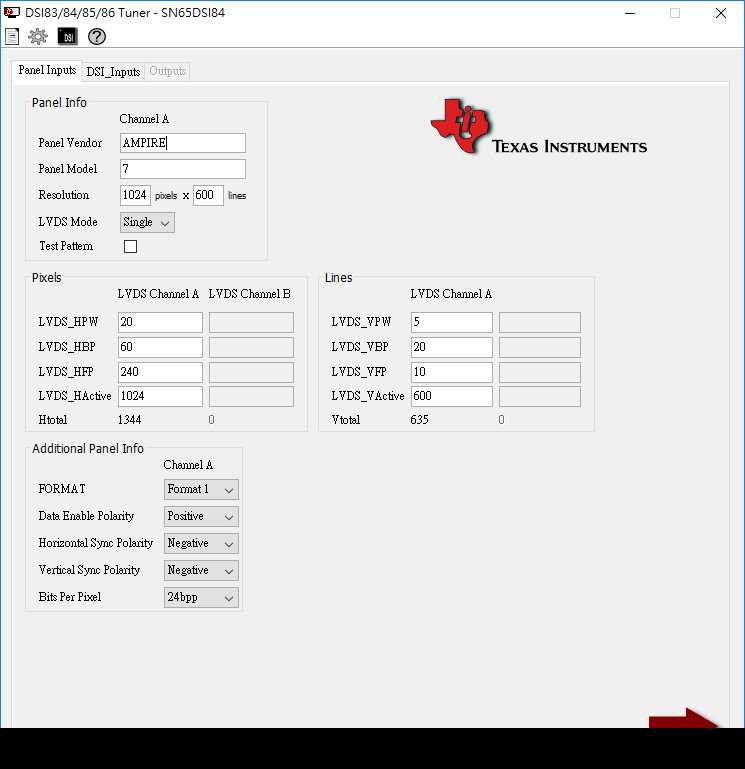

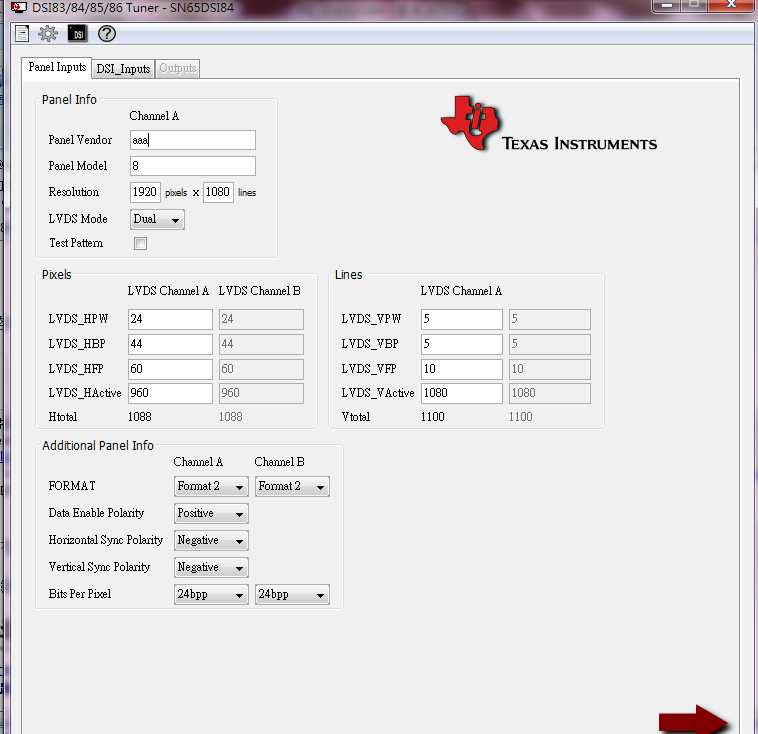

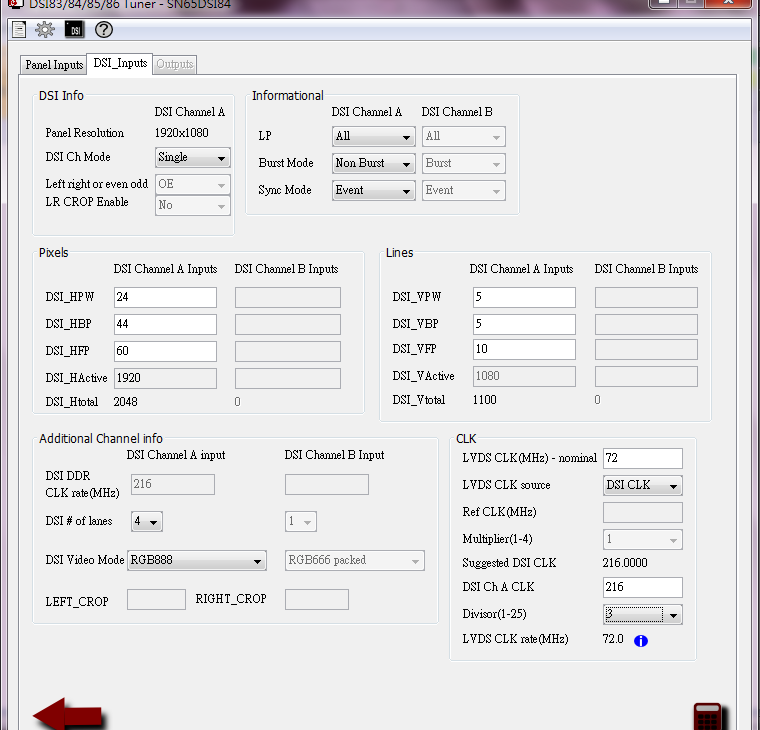

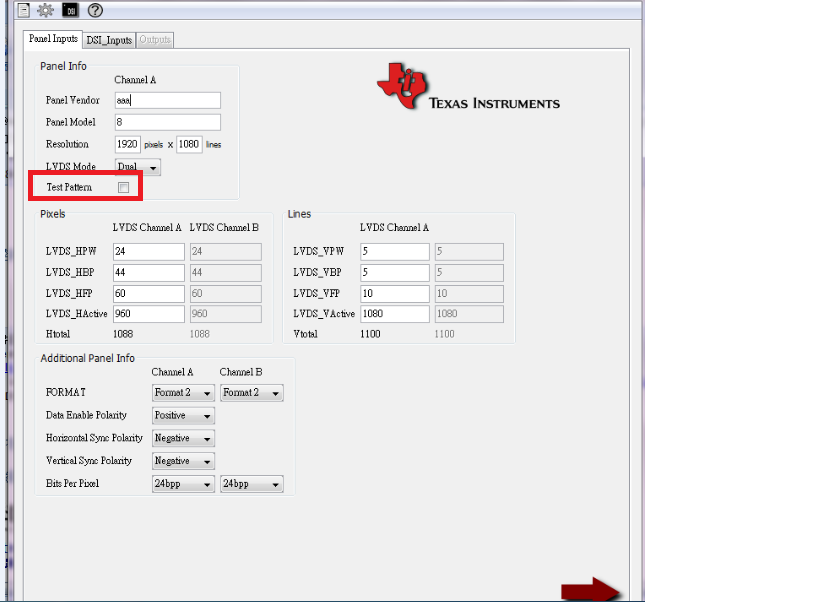

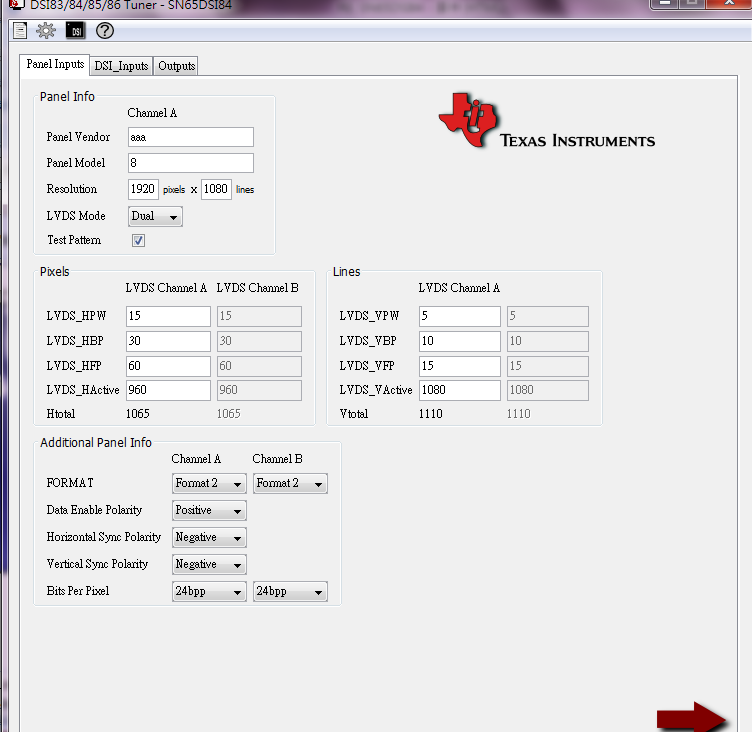

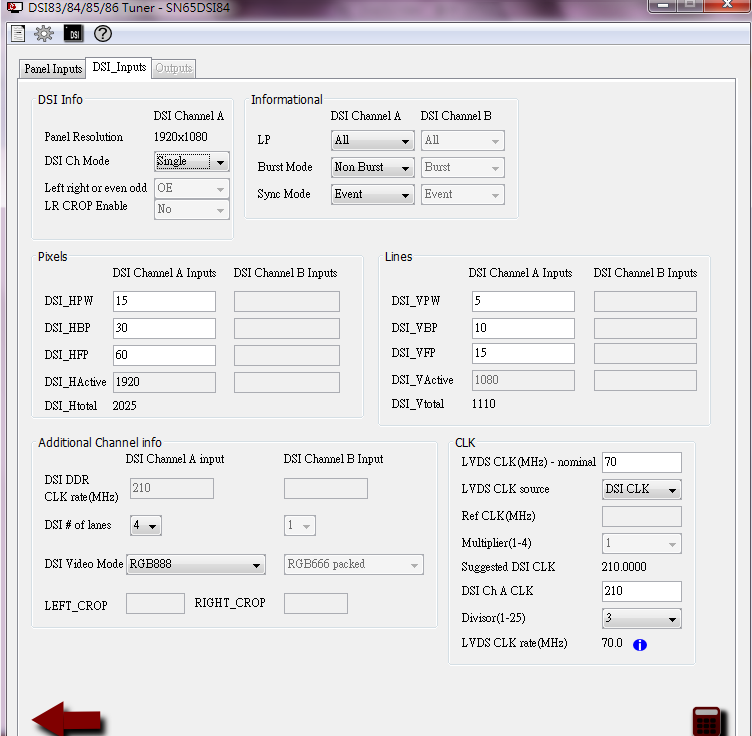

我们的设置如下

我们将把注册数据转移为我们的初始代码。

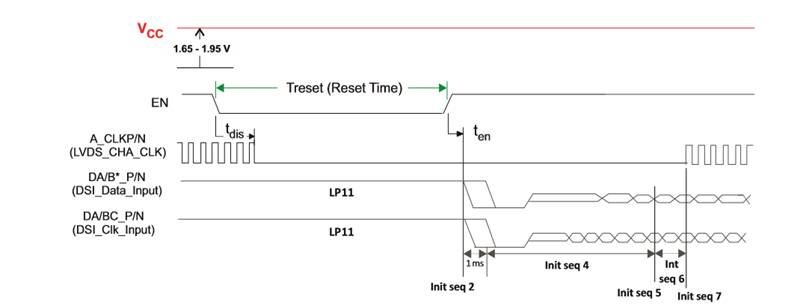

有来自MIPI侧的信号输出,CLK也是正常的。

但是只有Y2/CLK在DSI84端有输出,Y0/Y1/Y3没有。

CLK结果与我们的设置相同。

1.我们想知道 为什么Y0/Y1/Y3上没有输出?

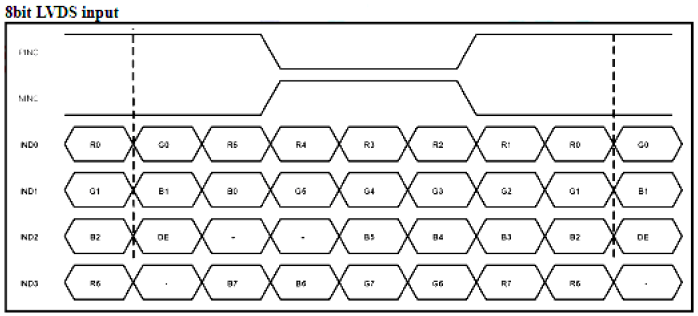

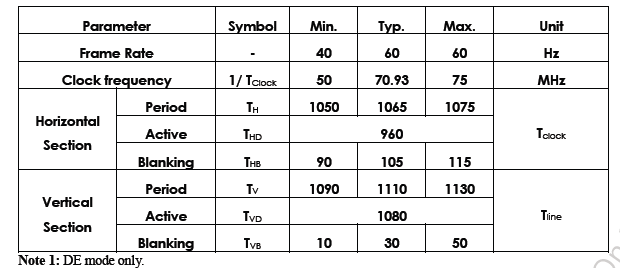

2. DSI84是否支持LVDS格式,如下所示?

如果是,如何设置? 如果否,是否有其他解决方案可以共享?

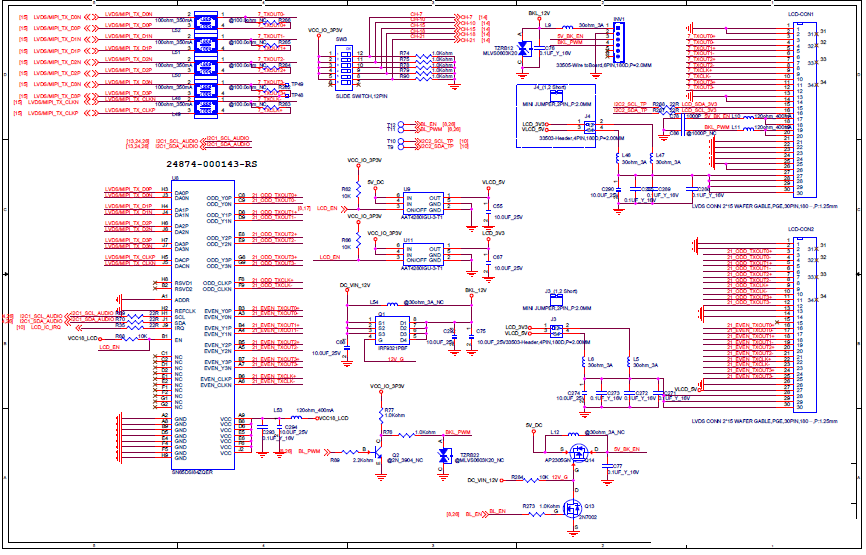

我们的原理图:

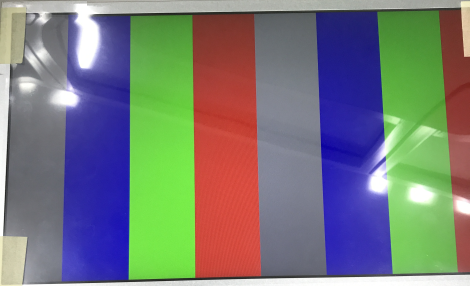

顺便说一下 ,DSI84测试模式已通过。

谢谢!!