主题中讨论的其他部件: DS90UB934-Q1

大家好,

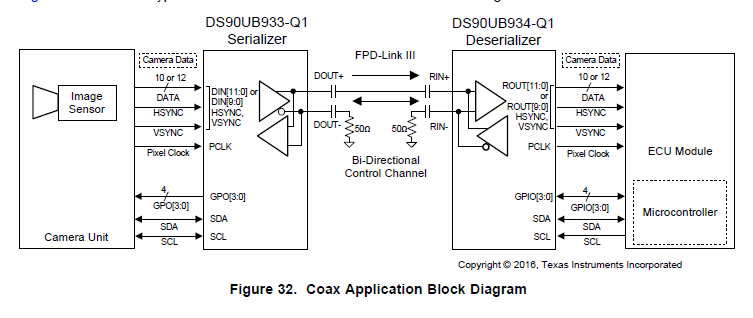

在我们的应用中,使用ds90ub933和ds90ub934通过同轴电缆传输视频信号,方框图如下所示

有关来自传感器的视频信号的详细信息如下所示

格式:12位 pclk:74.25M分辨率:1290 x 960

从CPU到串行器/解串器/摄像机的所有控制通道(I2C)访问都是正常的。

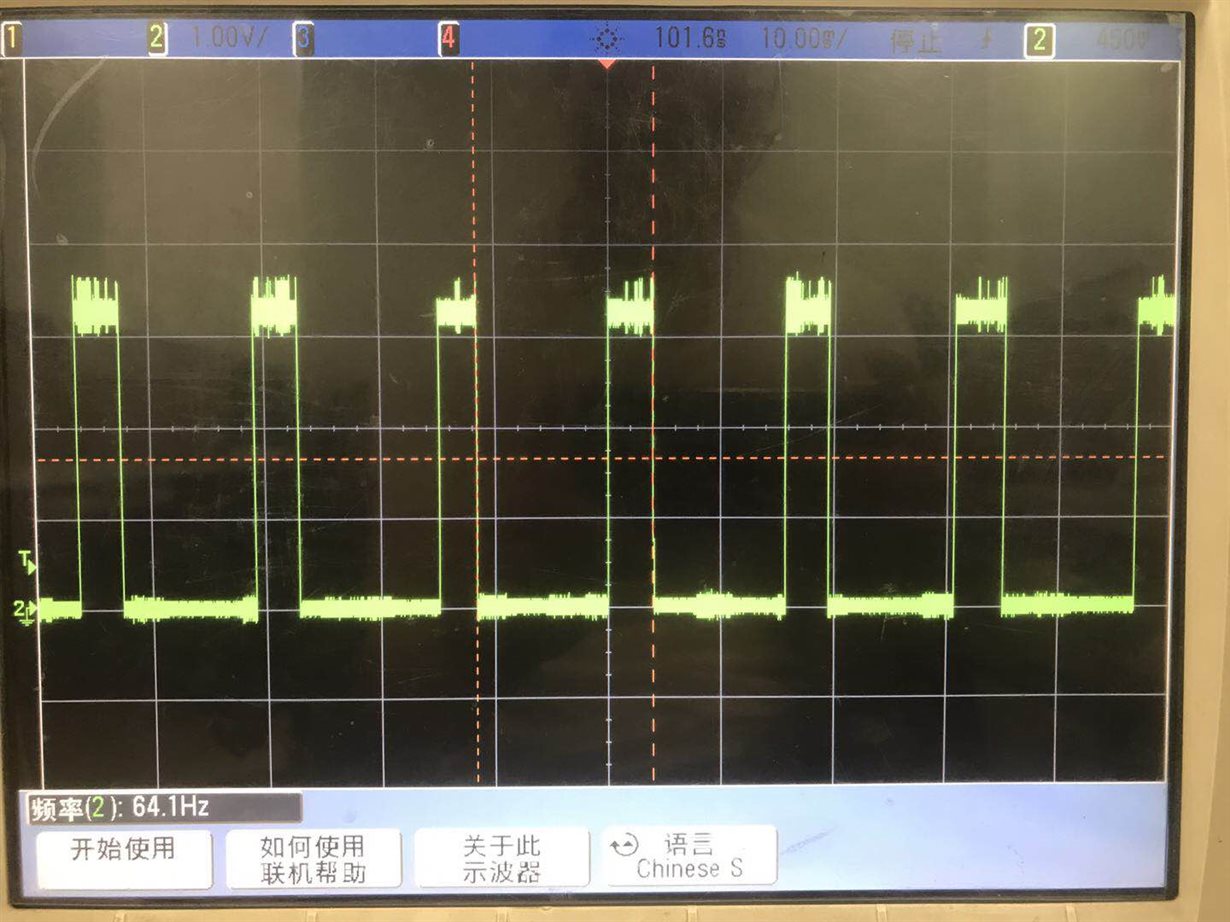

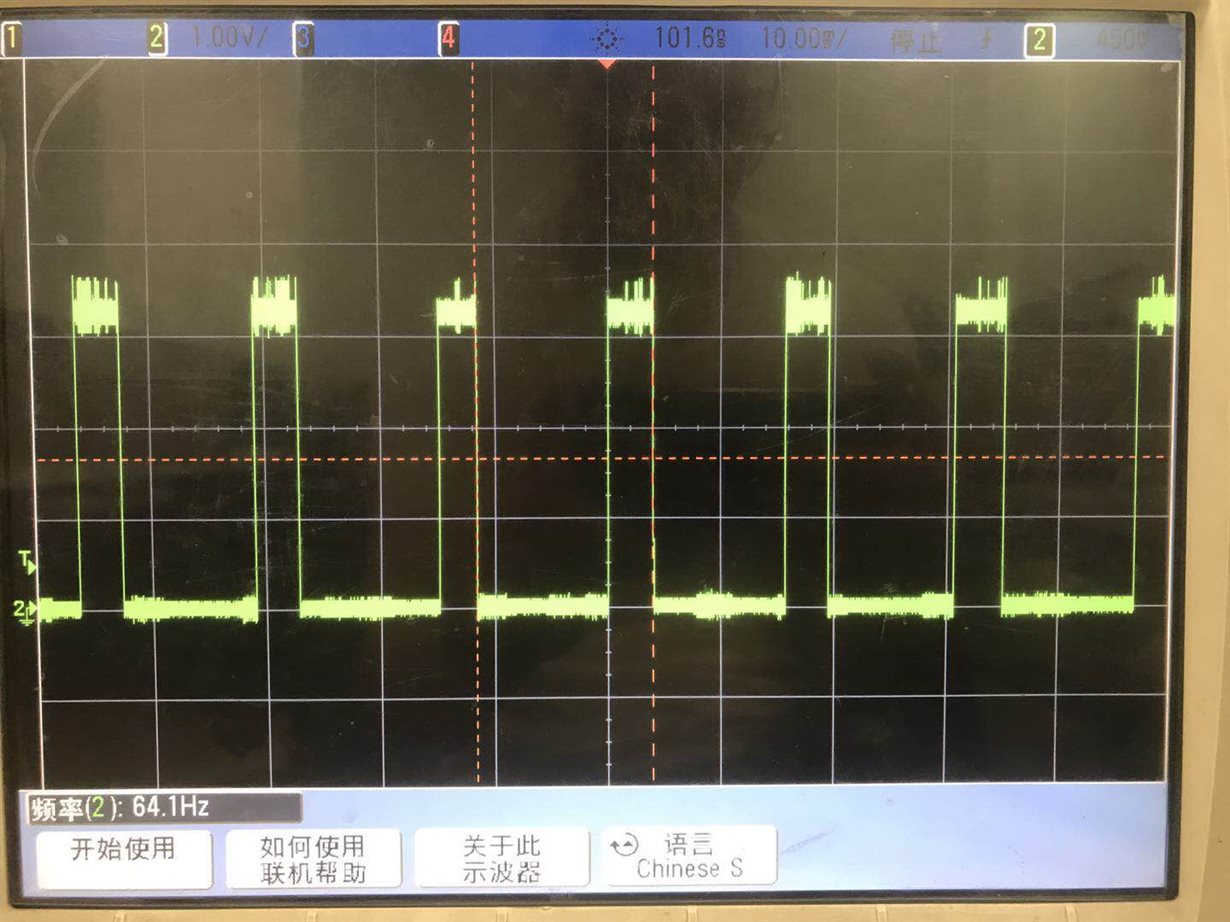

传感器开始工作后,我们可以测试传感器侧的pclk信号正常,但CPU侧以及ds90ub933侧似乎异常。

阅读有关ds90ub933的数据表时, 我们对以下内容有些怀疑。

7.3 2 DS90UB933/934的线速计算

DS90UB933-Q1器件在10位模式下将时钟内部除以2,在1.5 内部除以

12位模式。 相反,DS90UB934-Q1将恢复的串行时钟相乘以生成正确的

像素时钟输出频率。 以下是用于计算中最大线速的公式

不同模式:

•对于12位模式,线路速率=ƒPCLK×(2/3)×28;例如,ƒPCLK = 100 MHz,线路速率=(100 MHz)×

(2/3)×28 = 1.87 Gbps

•对于10位模式,线路速率=ƒPCLK /2×28;例如,ƒPCLK = 100 MHz,线路速率=(100 MHz/2)×28 =

1.40 Gbps

我的问题

如果来自传感器的pclk为74.25M, 则来自DS90UB934-Q1的pclk输出仍应为74.25M,而不是(74.25M / 1.5),对吗?

但是,在我们的应用中,我们可以监控 DS90UB933-Q1侧的pclk为74.25M,但 DS90UB934-Q1侧的pclk为 74.25M / 1.5 ,而不是预期 的74.25M。

DS90UB934-Q1似乎 无法恢复串行时钟以生成正确 的像素时钟输出频率?