Other Parts Discussed in Thread: LMH0344, LMH0041

主题中讨论的其他部件:LMH0344,

大家好。

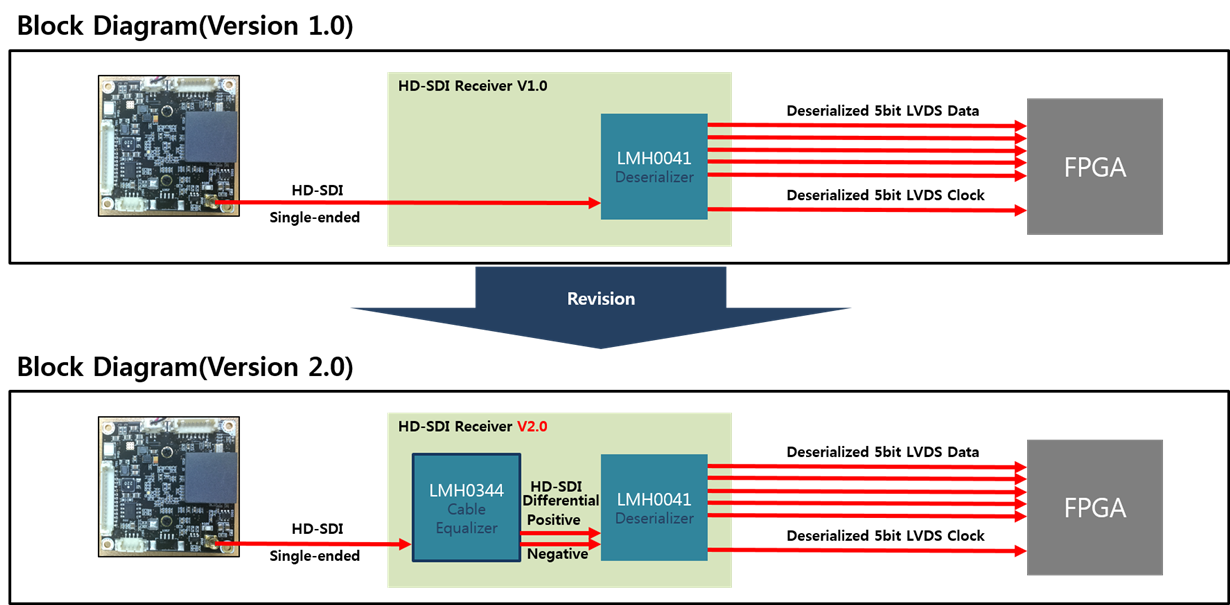

我设计了下面2个版本的HD-SDI DES (接收器)板。

但这并不是都能很好地发挥作用。

FPGA (Zed板)未能很好地识别LVDS信号。

我想知道什么是错误的。

请参阅以下详细信息。

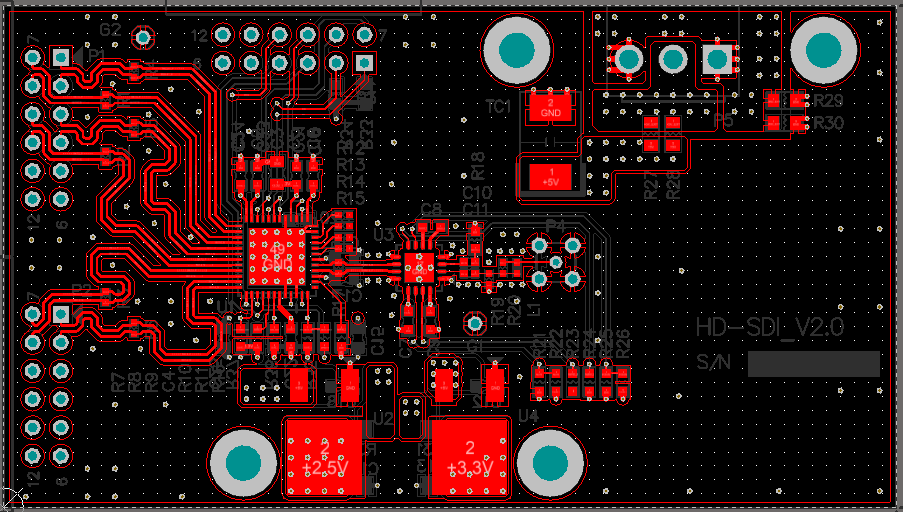

2.0 印刷电路板顶部

LVDS输出跟踪阻抗在PCB上为100欧姆(差分)。

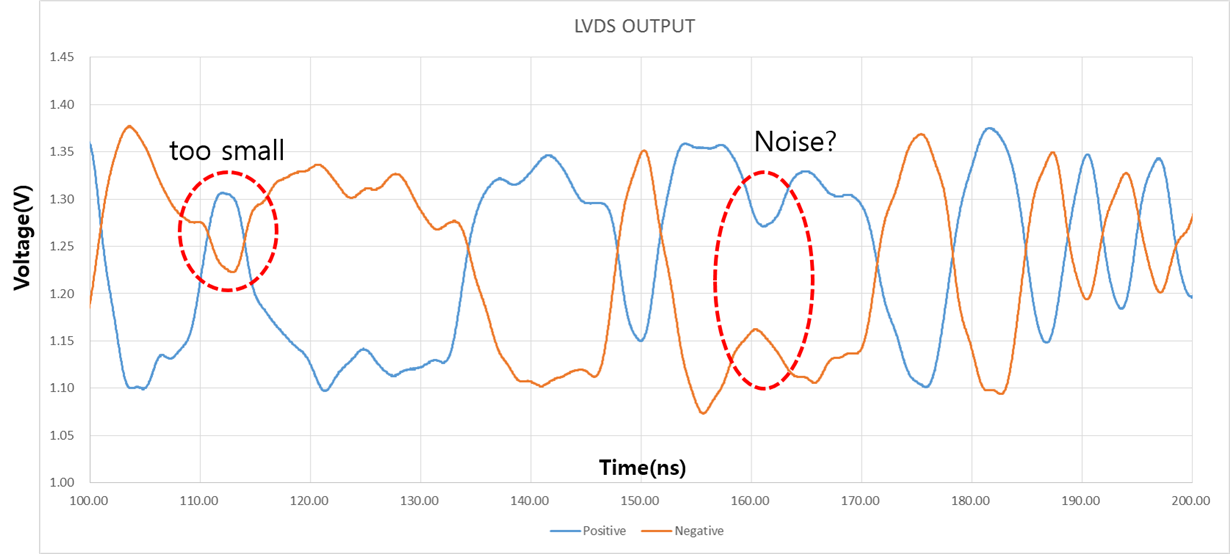

FPGA未识别LVDS信号。 (Zed板)

LVDS数据输出太奇怪,如下所示。

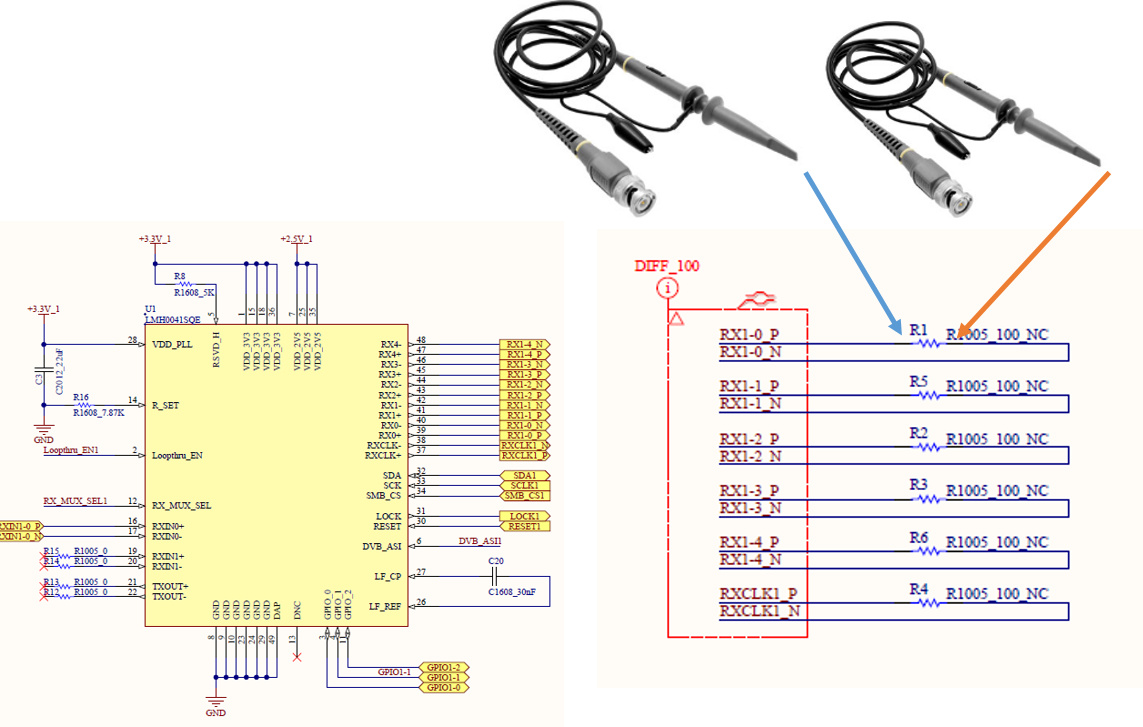

测量环境

* C20使用27nF而不是30nF。