主题中讨论的其他部件:TLK1.0022万

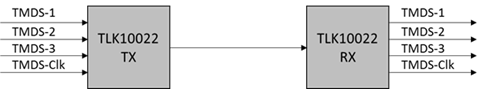

我们将使用TLK1002对HDMI/DVI信号的TMDS线路执行序列化/反序列化, 但有几个问题:

1. TLK1.0022万数据表的计时示例显示高速线侧速率为低速线侧速率的4倍(4:1),3倍(3:1)或2倍(2:1)。

如果使用8b/10b编码器,是否应按照10/8 系数乘以高速线路侧?

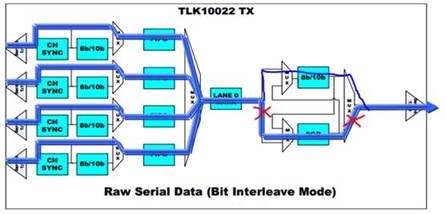

是否支持位交错模式和8b/10b编码?

2. 我的应用是DVI接口TMDS信号聚合/去聚合。 由于TMDS由3个数据信号(RGB组件)及其同步像素时钟组成,因此它并不是串行通道的聚合,但我认为它可以通过以下两种方式实现:

A) 要在4:1位交错模式下使用TLK1.0022万,并将像素时钟信号插入为第四条通道:

TMDS时钟频率为TMDS信号数据速率的1/10,因此可以将其视为1/5数据速率信号。 ¿TMDS-Clk是否可以在TLK1.0022万-Tx设备上过采样,然后在TLK1.0022万-Rx设备中恢复?

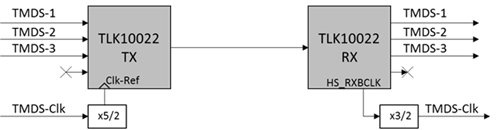

B) 要以3:1模式使用TLK1.0022万,请强制像素时钟作为高速线路侧时钟的参考,并从RX恢复时钟再次生成像素时钟:

IE:分辨率XGA (1024x768@60Hz)=> TMDS_SIGNALS数据速率= 0,65Gbps,TMDS_Clock = 65MHz。

低速SERDES (0,65Gbps)应以四分之一的速度工作,高速SERDES (1,95Gbps)也应以四分之一的速度工作。 低速PLL乘法器可以是8倍,高速PLL可以是12倍。

因此,所需的参考时钟将为(0,65Gbps x 2/8)=(TMDS_Clock x 5/2)。

在RX上,我们可以使用HS_RXBCLK = High_speed_data_rate /20,然后再次生成TMDS_clock = HS_RXBCLK x3/2。

TLK10.0022万在此应用程序中是否正常工作? 您能否提供任何建议?

提前感谢

Gabriel Cutillas