主题中讨论的其他部件: SN65DSI83

你好。

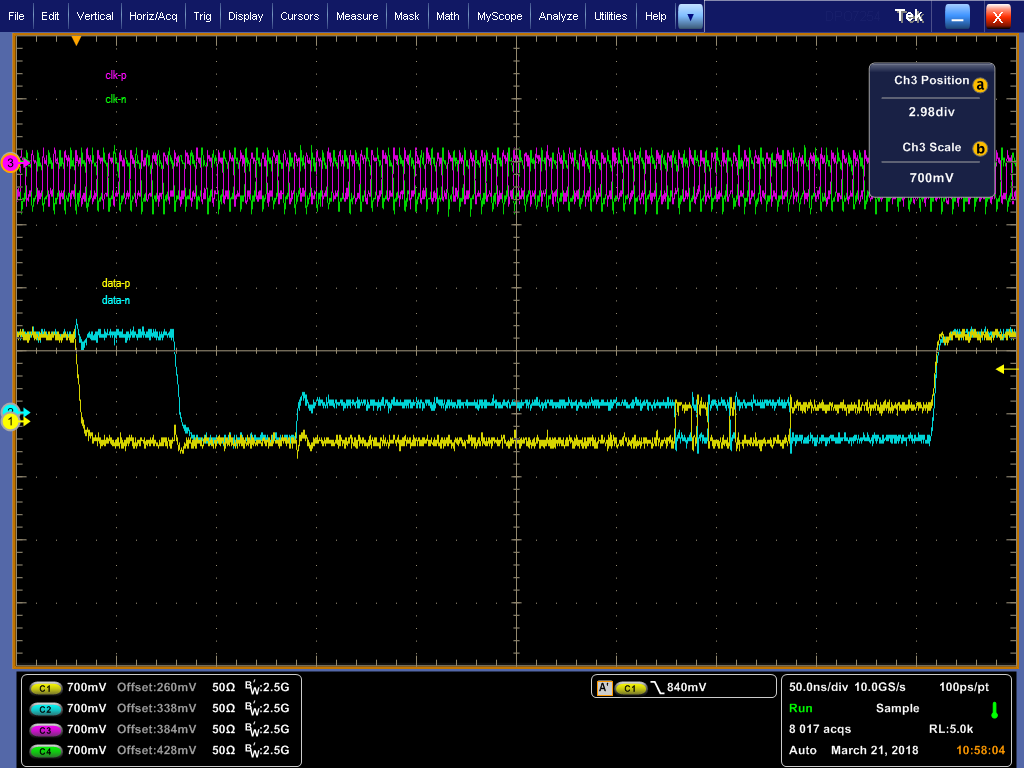

测试条件。

LCD:800*480

使用mipi 2lane,24bpp

LVDS时钟由面板定义为30MHz。

DSI时钟为180MHz。

CPU:MSM8974

MSM8974 MIPI <-> SN65DSI83Q1-EVM

DSI通道A <-> LVDS通道B <-> LCD面板

SN65DSI83寄存器控制不会更改屏幕。LVDS数据和时钟不会输出。

您能否检查代码。这是什么问题?

{0x09,0x00},// soft_reset

{0x0D,0x00},// PLL禁用

{0x0A,0x01},// LVDS OUT时钟范围(25-30-47)MHz =001, src clock from mipi dphy=1

{0x0B,0x10},// DSI时钟(像素clk = 30Mhz ->30/30-> DSI分频器是3->LVDS输出clk =30

{0x10, 0x10},// 800*480需要2个通道0x10

{0x11, 0x00},

{0x12,0x24},// cha dsi pixel时钟* bpp / 5000 = 3万 * 6 / 5000 = 36 => 30Mhz

{0x18, 0x6A},// 0x79 ->单通道,24位模式,hs/vs低,DE高:0x7F

{0x19, 0x00},

{0x1A,0x02},//默认值(0x03 -> 0x02)

{0x1B , 0x00},

{0x20,0x20},//宽度= 800 ->下部(0x20) 0x0320

{0x21,0x03},//宽度= 800 ->上部(0x03) 0x0320

{0x22,0x20},//宽度= 800 ->上部(0x03) 0x0320

{0x23,0x03},//宽度= 800 ->上部(0x03) 0x0320

{0x24,0xe0},//高度= 480 ->下部(0xe0) 0x01e0

{0x25,0x01},//高度= 480 ->下部(0x01) 0x01e0

{0x26, 0xe0},//高度=480 ->下部(0x01) 0x01e0

{0x27, 0x01},//高度=480 ->下部(0x01) 0x01e0

{0x28, 0x30},//通道A:同步延迟低,hblank =160,vblank =48,48(0x30) 0x21 -> 0x30

{0x29,0x00},//同步延迟高

{0x2A,0x30},//通道b

{0x2B,0x00},

{0x2C,0x10},//通道A:HSYNC脉冲宽度低(0x10=16)

{0x2d,0x00},// HSYNC脉冲宽度高(0x10=16)

{0x2E , 0x10},//通道b:

{0x2F , 0x00},

{0x30, 0x04},//通道A:垂直同步脉冲宽度低(0x04)

{0x31, 0x00},// vsync脉冲宽度高(0x04)

{0x32, 0x04},//通道b:

{0x33, 0x00},

{0x34, 0x48},//通道A:水平后廊=72(0x48)

{0x35, 0x48},//通道b:水平后廊=72(0x48)

{0x36, 0x16},//通道A:垂直后廊=22(0x16)

{0x37, 0x16},//通道b:

{0x38, 0x48},//通道A:水平前廊=72(0x48)

{0x39, 0x48},//通道b:

{0x3A,0x16},//通道A:垂直前廊=22(0x16)

{0x3B,0x16},//通道b:

{0x3C,0x00},//测试模式

{0x3D , 0x00},

{0x3E , 0x00},

{REG_ENDFLAG,0x00},//结束标志

{0x09, 0x01},//软复位

{REGFLAG_DELAY,10},// PLL稳定延迟

{0x0D,0x01},// PLL_EN

{REG_ENDFLAG,0x00},//结束标志

谢谢,此致

Downey Kim。