工具/软件:Linux

TI专家,您好!

我们正在为客户调试Android PAD项目。

此项目与 以前的设计不同。 在以前的设计中,CPU是Qualcomm MSM8939,LCD显示屏使用MIPI DSI接口,一切正常。

新设计将LCD显示接口更改为LVDS (扁平链路)。 因此,连接是MSM8939 -> SN65DSI83 -> LVDS LCD显示屏。 SN65DSI83使用MIPI D-PHY时钟作为时钟源。

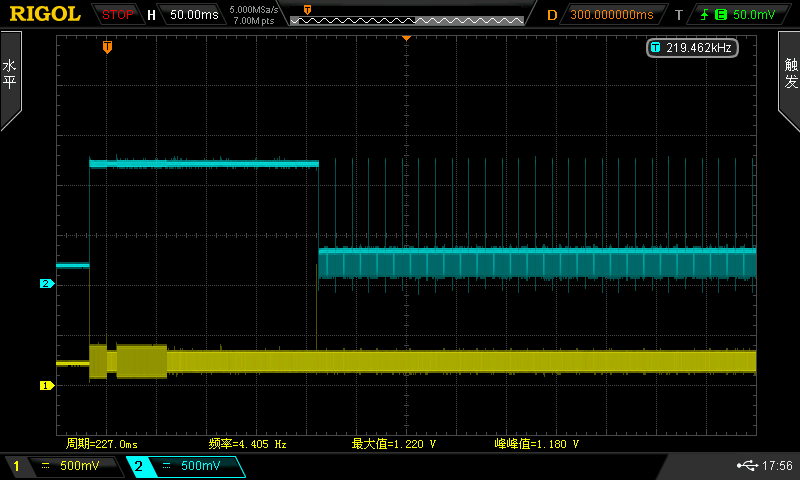

我们已经做出了巨大的努力来使液晶显示屏正常工作。 我们一直在使用SN65DSI83的测试模式功能测试硬件,最后将D-PHY时钟更改为连续模式,我们成功了。 SN65DSI83的测试模式如下:

通过查看测试模式,我们相信时钟正常(我们使用示波器显示D-PHY和LVDS的时钟,两者都正确),LCD显示屏的参数是匹配的。但是, 通过关闭测试模式功能,我们仍然无法在LCD中看到任何输出。 已经审查了MIPI DSI的计时参数,似乎很好。

LCD分辨率为1280x800,MIPI D-PHY时钟为200MHz, 在我们的设置中,我们将其除以4作为LVDS时钟。

测试模式的SN65DSI83寄存器设置 以HTML脚本编写,可在附件中找到。

请给出一些建议,是否还有其他事情需要考虑? e2e.ti.com/.../SN65DSI83_5F00_D101AXHDIF_2D00_CC003_5F00_Qualcomm_5F00_TestPatern.xml