Other Parts Discussed in Thread: PCA9306-Q1

大家好,

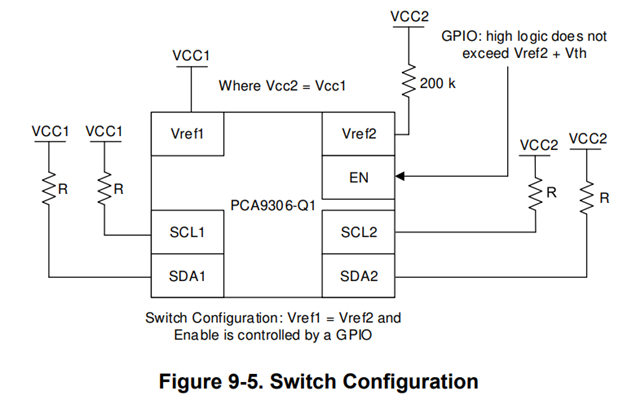

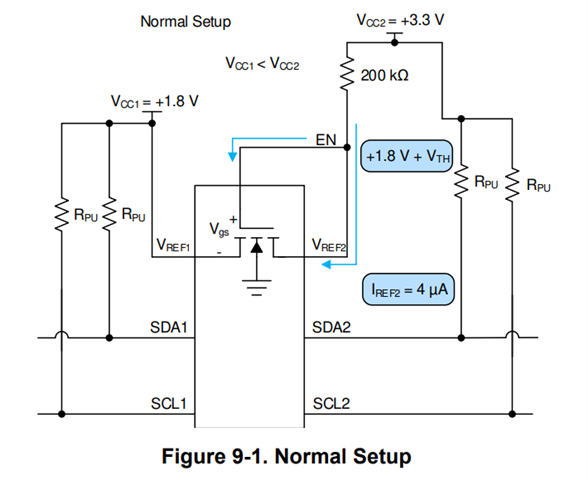

我的客户使用 PCA9306-Q1作为I2C开关,而VREF1=VREF2=1.8V。 我对 EN引脚的电压选择有疑问。 为什么我们不能选择高逻辑来超过Vref2+Vth? 我的理解是,这将有助于减少内部FET的RDS (接通)。 在这种情况下(VREF1=VREF2=1.8V),VREF1和VREF2之间的电流不会过大。

VREF1和VREF2之间内部FET的作用是什么? 是否仅用于启动? sda1&sda2/SCL1&SCL2之间还有另外两个FET,对吗?

巴西,

唐英年