主题中讨论的其他器件:DP83869、 DP83869EVM

我在定制 PCB 上安装了此 PHY、该 PCB 通过 SGMII 与 Intel FPGA 连接。 PHY 连接到支持1000BASE-T 的 Bel MagJack 我将部件设置为 SGMII 至 Copper 模式、自动协商、通告1000/100/10和自动 MDI-X 我已经通过 MDIO 确认了此配置。 自协商不会在1000M 连接、而是选择100M。 我正在寻求帮助、以排除无法建立1000M 连接的原因。

谢谢你

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我在定制 PCB 上安装了此 PHY、该 PCB 通过 SGMII 与 Intel FPGA 连接。 PHY 连接到支持1000BASE-T 的 Bel MagJack 我将部件设置为 SGMII 至 Copper 模式、自动协商、通告1000/100/10和自动 MDI-X 我已经通过 MDIO 确认了此配置。 自协商不会在1000M 连接、而是选择100M。 我正在寻求帮助、以排除无法建立1000M 连接的原因。

谢谢你

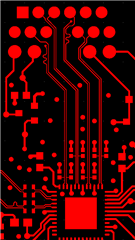

链路伙伴是连接到 Windows PC 的千兆交换机。 我们拥有此定制 PCB 的早期版本、该版本能够通过开关以1000M 的速度连接到该 PC。 我在这个帖子的末尾附加了寄存器转储。 我还连接了该 PHY 的原理图页面以及 PHY 和插孔之间连接的光绘文件。 注意事项:

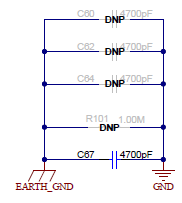

1) 1) MDI 线路上的端接电阻器网络是上一个电路板的伪影。 我认为这些应该删除、但我不确定这是否会导致1000M 无法正常工作?

2) 2)两条 MDI 线路上有不匹配的过孔、这会导致差分对线路之间的电容差~1pF、但我不认为延迟会导致这种情况不起作用?

3) 3)我的 MDI 差分对长度匹配、但4个通道的长度不匹配。

4) 4)我们没有任何电路保护、因为该板连接到开关、而不是外部世界。

我正在浏览 DP83867故障排除指南、如果发现任何其他信息、我将更新此帖子。

谢谢、

Dan

e2e.ti.com/.../Ethernet-Page.pdf

BMCR 4416

BMSR 31081

PHYIDR1 8192

PHYIDR2 41201

Anar 481

ALNPAR 50657

ANER 111

ANNPTR 8193

ANLNPTR 30721

Gen_CFG1 2816

Gen_Status1 0

REGCR 16415

地址4416

ONEKSCR 61440

PHY_CONTROL 20552

PHY_STATUS 31746

INTERRUPT_MASK 0

INTERRUPT_STATUS 23874

Gen_CFG2 10695

RX_ERR_CNT 0

BIST_CONTROL 0

Gen_STATUS2 64

LEDS_CFG1 24912

LEDS_CFG2 17476

LEDS_CFG3 2.

Gen_CFG4 18.

GEN_CTRL 0

ANALOG_TEST_CTRL 0

GEN_CFG_ENH_AMIX 0

GEN_CFG_FLD 0

GEN_CFG_FLD_THR 0

Gen_CFG3 0

RGMII_CTRL 80

RGMII_CTRL2 0

SGMII_AUTO_NEG_STATUS 3.

PRBS_TX_CHK_CTRL 0

PRBS_TX_CHK_BYTE_COUNT 0

G_100BT_REG0 1952

SerDes_SYNC_STS 278

Strap 3072

ANA_RGMII_DLL_CTRL 119

RXF_CFG 4096

RXF_STATUS 0

IO_MUX_CFG 3088

TDR_GEN_CFG1 1874

TDR_GEN_CFG2 51280

TDR_SEG_Duration1 21286

TDR_SEG_DURATION2 40990

TDR_GEN_CFG3 59766

TDR_GEN_CFG4 6607

TDR_peaks LOC_A_0_1 0

TDR_peaks LOC_A_2_3 0

TDR_peaks LOC_A_4_B_0

TDR_peaks LOC_B_1_2 0

TDR_peaks LOC_B_3_4 0

TDR_peaks LOC_C_0_1 0

TDR_peaks LOC_C_2_3 0

TDR_peaks _LOC_4_D_0

TDR_peaks LOC_D_1_2 0

TDR_peaks LOC_D_3_4 0

TDR_GEN_STATUS 0

TDR_peaks 符号_A_B 0

TDR_peaks _符号_C_D 0

OP_MODE_DECODE 70

GPIO_MUX_CTRL 16762

FX_CTRL 4416

FX_STS 24937

FX_PHYID1 8192

FX_PHYID2 41201

FX_ANADV 32

FX_LPABL 16385

FX_ANEXP 3.

FX_LOCNP 8193

FX_LPNP 0

FX_INT_EN 511

FX_INT_STS 17.

Daniel、您好!

感谢您提供信息。 您列出的注释肯定会影响信号质量、但很难量化。 首先、我想确认这是自动协商问题、还是您怀疑的电路板设计/信号完整性问题。

您能否尝试将两个 DP83869电路板连接在一起? 如果它仍然以100Mbps 的速率上升、请尝试禁用两侧的自动协商并强制执行1000Mbps 操作。 那么会发生什么情况?

您能否告诉我、在尝试链接之前、您正在从默认设置更改哪些寄存器设置(如果有)?

让我知道这些问题的答案、然后在必要时、我可以更深入地回顾原理图和布局。

另外、请为我们提供 有关之前功能板的更多背景信息、而不是这种新的功能板。 所做的所有更改是什么?

谢谢、

David

我将详细介绍您关于直接连接两个板的建议。 如果我可以使用该器件执行任何调试活动、我刚刚在该器件的开发板中收到该信息。 同时、这里是您其他问题的答案。

1) 1) 您还能告诉我、在尝试链接之前、您要从默认设置更改哪些寄存器设置(如果有)?

这些寄存器是根据数据表的第9.4.8.6节进行配置的。 寄存器0x01DF 设置为复位值、但对于 SGMII 到 Copper 的位2-0则设置为0x6。

2) 2)另请为我们提供 有关之前功能板的更多背景信息、而不是这一新功能板的背景信息。 所做的所有更改是什么?

这是电路板的完全重新设计、其中包括新的以太网插孔、磁性元件、PHY 和 FPGA。 之前的 PHY 是 Marvell 88E1111、它配置为通过 RGMII 与 FPGA 连接、该器件设置为广播10/100/1000Mb。 在两个系统中、链路伙伴保持不变。

谢谢、

Daniel

David、

这是两个板相互连接时的寄存器读数。 PHY_STATUS 寄存器指示后面1000Mb 的速度。 我还重复了与开发板相连的测试、测试结果还表明、之后的连接速度为1000Mb。

谢谢、

Daniel

BMCR 4416

BMSR 31085.

PHYIDR1 8192

PHYIDR2 41201

Anar 481

ALNPAR 49633

ANER 111

ANNPTR 8193

ANLNPTR 18432

Gen_CFG1 2816

Gen_Status1 15360

REGCR 16415

地址4416

ONEKSCR 61440

PHY_CONTROL 20552

PHY_STATUS 44802

INTERRUPT_MASK 0

INTERRUPT_STATUS 7488

Gen_CFG2 10695

RX_ERR_CNT 0

BIST_CONTROL 0

Gen_STATUS2 64

LEDS_CFG1 24912

LEDS_CFG2 17476

LEDS_CFG3 2.

Gen_CFG4 18.

GEN_CTRL 0

ANALOG_TEST_CTRL 0

GEN_CFG_ENH_AMIX 0

GEN_CFG_FLD 0

GEN_CFG_FLD_THR 0

Gen_CFG3 0

RGMII_CTRL 80

RGMII_CTRL2 0

SGMII_AUTO_NEG_STATUS 3.

PRBS_TX_CHK_CTRL 0

PRBS_TX_CHK_BYTE_COUNT 0

G_100BT_REG0 1952

SerDes_SYNC_STS 326

Strap 3072

ANA_RGMII_DLL_CTRL 119

RXF_CFG 4096

RXF_STATUS 0

IO_MUX_CFG 3084

TDR_GEN_CFG1 1874

TDR_GEN_CFG2 51280

TDR_SEG_Duration1 21286

TDR_SEG_DURATION2 40990

TDR_GEN_CFG3 59766

TDR_GEN_CFG4 6607

TDR_peaks LOC_A_0_1 0

TDR_peaks LOC_A_2_3 0

TDR_peaks LOC_A_4_B_0

TDR_peaks LOC_B_1_2 0

TDR_peaks LOC_B_3_4 0

TDR_peaks LOC_C_0_1 0

TDR_peaks LOC_C_2_3 0

TDR_peaks _LOC_4_D_0

TDR_peaks LOC_D_1_2 0

TDR_peaks LOC_D_3_4 0

TDR_GEN_STATUS 0

TDR_peaks 符号_A_B 0

TDR_peaks _符号_C_D 0

OP_MODE_DECODE 70

GPIO_MUX_CTRL 16762

FX_CTRL 4416

FX_STS 24937

FX_PHYID1 8192

FX_PHYID2 41201

FX_ANADV 32

FX_LPABL 16385

FX_ANEXP 3.

FX_LOCNP 8193

FX_LPNP 0

FX_INT_EN 511

FX_INT_STS 17.

David、

第一个寄存器转储是在电路板连接到开关时进行的。 以下是几个数据点、使我相信它不是链接伙伴:

谢谢、

Daniel

数据传输之前的寄存器转储

BMCR 4416

BMSR 31081

PHYIDR1 8192

PHYIDR2 41201

Anar 481

ALNPAR 50657

ANER 111

ANNPTR 8193

ANLNPTR 22534

Gen_CFG1 2816

Gen_Status1 10240

REGCR 16415

地址4416

ONEKSCR 61440

PHY_CONTROL 20552

PHY_STATUS 47874

INTERRUPT_MASK 0

INTERRUPT_STATUS 23874

Gen_CFG2 10695

RX_ERR_CNT 0

BIST_CONTROL 0

Gen_STATUS2 64

LEDS_CFG1 24912

LEDS_CFG2 17476

LEDS_CFG3 2.

Gen_CFG4 18.

GEN_CTRL 0

ANALOG_TEST_CTRL 0

GEN_CFG_ENH_AMIX 0

GEN_CFG_FLD 0

GEN_CFG_FLD_THR 0

Gen_CFG3 0

RGMII_CTRL 80

RGMII_CTRL2 0

SGMII_AUTO_NEG_STATUS 3.

PRBS_TX_CHK_CTRL 0

PRBS_TX_CHK_BYTE_COUNT 0

G_100BT_REG0 1952

SerDes_SYNC_STS 294

Strap 3072

ANA_RGMII_DLL_CTRL 119

RXF_CFG 4096

RXF_STATUS 0

IO_MUX_CFG 3088

TDR_GEN_CFG1 1874

TDR_GEN_CFG2 51280

TDR_SEG_Duration1 21286

TDR_SEG_DURATION2 40990

TDR_GEN_CFG3 59766

TDR_GEN_CFG4 6607

TDR_peaks LOC_A_0_1 0

TDR_peaks LOC_A_2_3 0

TDR_peaks LOC_A_4_B_0

TDR_peaks LOC_B_1_2 0

TDR_peaks LOC_B_3_4 0

TDR_peaks LOC_C_0_1 0

TDR_peaks LOC_C_2_3 0

TDR_peaks _LOC_4_D_0

TDR_peaks LOC_D_1_2 0

TDR_peaks LOC_D_3_4 0

TDR_GEN_STATUS 0

TDR_peaks 符号_A_B 0

TDR_peaks _符号_C_D 0

OP_MODE_DECODE 70

GPIO_MUX_CTRL 16762

FX_CTRL 4416

FX_STS 24937

FX_PHYID1 8192

FX_PHYID2 41201

FX_ANADV 32

FX_LPABL 16385

FX_ANEXP 3.

FX_LOCNP 8193

FX_LPNP 0

FX_INT_EN 511

FX_INT_STS 49

Daniel、您好!

您在最新帖子中的"定制 PCC"是什么意思?

下面是我要尝试的几个实验:

1.尝试禁用速度优化位并查看 行为是什么。 如果不执行任何操作、则恢复为默认值。

2.使用 dp83869将您的定制板连接到您现有的任何其他链接伙伴。 所有这些都是失败的吗?

3.禁用自动协商并使用 BMCR 寄存器强制定制电路板上的1000Mbps 操作。 在开关侧强制运行1000Mbps。

4. 将我们的869EVM 连接到您的交换机。

请告诉我结果。 此外、是否可以发送十六进制格式的任何未来寄存器转储?

谢谢、

David

David、

定制 PCB 是带有 dp83869器件的定制板、很抱歉造成混淆。

1.行为保持不变。 已通过并选择1000Mb、但无法连接和传输数据。 我们看到发送了少量数据包、然后连接中断。 我已连接该寄存器转储。

2.定制板无法连接到我们在1000Mb 尝试的任何连接伙伴(切换/直接连接 至 Windows PC/USB 至以太网适配器/面板 PC)。

3.我们没有看到使用此配置的流量。 我们将继续研究这一点、并尝试其他速度以确认我们的手动配置是否正确实施。

4.我已从连接到交换机的869EVM 连接了一个寄存器转储。

谢谢、

Daniel

e2e.ti.com/.../869EVM_5F00_to_5F00_Switch.txt

寄存器转储-无速度优化

BMCR 0x1140

BMSR 0x796d

PHYIDR1 0x2000

PHYIDR2 0xa0F1

Anar 0x1e1

ALNPAR 0xcde1

ANER 0x6f

ANNPTR 0x2001

ANLNPTR 0x4006

Gen_CFG1 0xb00

Gen_Status1 0x7800

REGCR 0x401f

地址0x1140

ONEKSCR 0xf000

PHY_CONTROL 0x5048

PHY_STATUS 0xaf02

INTERRUPT_MASK 0x0

INTERRUPT_STATUS 0x1c42

Gen_CFG2 0x28c7

RX_ERR_CNT 0x0

BIST_CONTROL 0x0

GEN_STATUS2 0x40

LEDS_CFG1 0x6150

LEDS_CFG2 0x4444

LEDS_CFG3 0x2

Gen_CFG4 0x12

GEN_CTRL 0x0

ANALOG_TEST_CTRL 0x0

GEN_CFG_ENH_AMIX 0x0

GEN_CFG_FLD 0x0

GEN_CFG_FLD_THR 0x0

Gen_CFG3 0x0

RGMII_CTRL 0x50

RGMII_CTRL2 0x0

SGMII_AUTO_NEG_STATUS 0x3

PRBS_TX_CHK_CTRL 0x0

PRBS_TX_CHK_BYTE_COUNT 0x0

G_100BT_REG0 0x7a0

SERDES_SYNC_STS 0x106

自举_STS 0xc00

ANA_RGMII_DLL_CTRL 0x77

RXF_CFG 0x1000

RXF_STATUS 0x0

IO_MUX_CFG 0xc0c

TDR_GEN_CFG1 0x752

TDR_GEN_CFG2 0xc850

TDR_SEG_Duration1 0x5326

TDR_SEG_DURATION2 0xa01e

TDR_GEN_CFG3 0xe976

TDR_GEN_CFG4 0x19CF

TDR_peaks _LOC_A_0_1 0x0

TDR_peaks LOC_A_2_3 0x0

TDR_peaks _LOC_A_4_B_0 0x0

TDR_peaks _LOC_B_1_2 0x0

TDR_peaks _LOC_B_3_4 0x0

TDR_peaks _LOC_0_1 0x0

TDR_peaks _LOC_2_3 0x0

TDR_peaks _LOC_4_D_0 0x0

TDR_peaks _LOC_D_1_2 0x0

TDR_peaks _LOC_D_3_4 0x0

TDR_GEN_STATUS 0x0

TDR_peaks 符号_A_B 0x0

TDR_peaks _签名_C_D 0x0

OP_MODE_DECODE 0x46

GPIO_MUX_CTRL 0x417A

FX_CTRL 0x1140

FX_STS 0x6169

FX_PHYID1 0x2000

FX_PHYID2 0xa0F1

FX_ANADV 0x20

FX_LPABL 0x4001

FX_ANEXP 0x3

FX_LOCNP 0x2001

FX_LPNP 0x0

FX_INT_EN 0x1ff

FX_INT_STS 0x11

Daniel、您好!

我可能 误解了这个问题。 因此、为了澄清这一点、 我看到定制 PCB 以1000Mbps 的速率启动、显示链路状态良好、显示自协商完成、如最新转储中的 PHY_STATUS 寄存器所示。 一段时间后、它会降至100Mbps? 下降需要多长时间?

"已通过、选择1000Mb、但无法连接和传输数据。 我们看到发送了几个数据包、然后连接中断"

您如何判断 PHY 未能连接和传输数据? 连接中断意味着它会降至100Mbps 还是链路中断? PHY 降至100Mbps 后、您是否看到流量?

我将查看您的原理图、下周将向您提出任何意见。

谢谢、

David

David、

您如何判断 PHY 未能连接和传输数据? 连接中断意味着它会降至100Mbps 还是链路中断? PHY 降至100Mbps 后、您是否看到流量?

我们使用 Wireshark 来监控以太网流量。 是的、我看到 PHY 下降到100Mbps 后流量持续。

因此、为了澄清这一点、 我看到定制 PCB 以1000Mbps 的速率启动、显示链路状态良好、显示自协商完成、如最新转储中的 PHY_STATUS 寄存器所示。 一段时间后、它会降至100Mbps? 下降需要多长时间?

是的、完全正确。 我认为、目前的情况是、它尝试以1000Mbps 的速率发送消息、然后由于速度优化而降至100Mbps。 当速度优化关闭时、我可以看到在链路断开之前发送了4-6个数据包。

谢谢、

Daniel

Daniel、您好!

下面是我对原理图的评论:

C58、C64、C72、C78应为10nF 而不是10uF

2.确保晶振规格符合 数据表10.2.1.2.1.1节中列出的要求

MDC 引脚不应有上拉电阻器

DP83869集成了 MDI 终端电阻器、因此不建议使用 R37-R44和 C90-C93。 添加此"保护"部分是否有原因?

5.建议添加将 MDI 连接器接地与数字接地隔离的选项,如 DP83869EVM 原理图所示。

谢谢、

David

Daniel、您好!

你是对的。 由于 EVM 上没有 MAC、因此您不会看到 TCP 数据包。 但是、由于您已确认 EVM 已连接并保持1000Mbps、因此可以放心地说 、此处的问题是定制板的原理图和/或布局。

请根据上面列出的注释以及数据表第12节和 以太网 PHY PCB 设计布局检查清单中描述的原理来更新电路板。 也可将我们的 EVM 原理图用作参考。

如果您有其他问题、请告诉我。

谢谢、

David