Other Parts Discussed in Thread: THVD8000, THVD8010

主题中讨论的其他器件: THVD8010

大家好、

我一直在进行一些测量,以预先符合铁路规范(在 1kHz、 150kHz 至80MHz 频率下,AM 为80%时,0Vrms 传导噪声) 和... 我无法通过: 1kHz 的振幅调制看起来像是 THVD8000的1kHz OOK 调制。

我的设置有一些问题,我知道这一点,但并非一切都能像我们希望的那样完美(即使在火车的最后实施中):

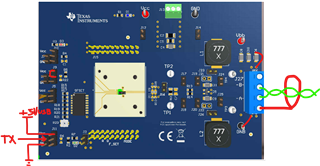

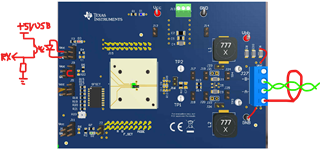

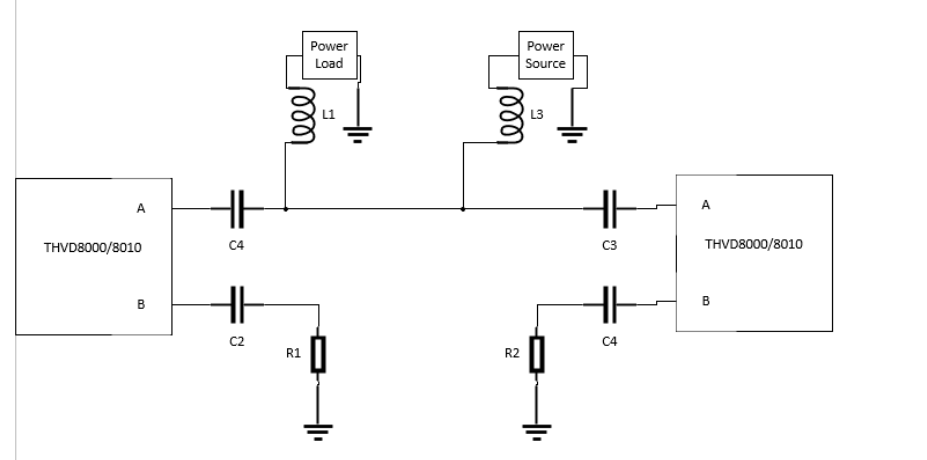

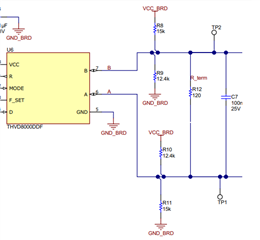

我使用的是2个 THVD8000评估模块、其中一个评估模块具有将 THVD 配置为始终 TX 的 USB-UART 适配器、5V USB 电源通过 PLC 组件为本地板和10m 远的电路板供电、 然后是一个10m 电缆环路、另一个 EVM 配置为始终 RX 、并 通过光耦合器将数据返回到初始 USB-UART 适配器(两个 EVM 背对背(彼此之间20mm)。

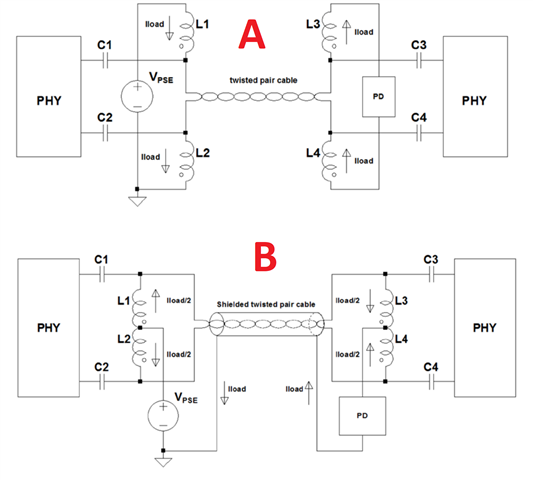

10Vrms 传导是在屏蔽电缆上完成的(没有符合120欧姆铁路标准的电缆、因为它将在列车中放置、因此我使用的是正常的屏蔽0.75mm² Ω 电缆)

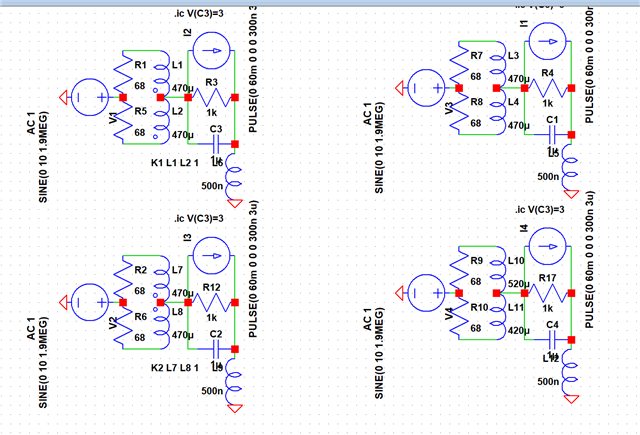

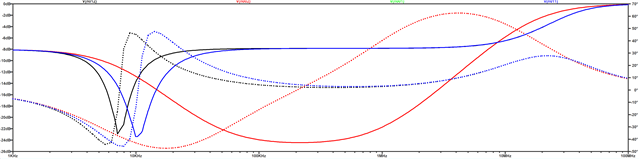

EVM 设置为5MHz 调制、共模噪声以某种方式转换为差分(拾取线圈变化+/-20%?) 在大约5和10MHz 下(这些基波和一次谐波周围为+/-20%)

我测试了用 PoE 变压器(Wurth 分离初级)替代 L-C 提取/注入的方法、但我从他们那里得到信息、如果与直流电流(具有差分电流、而非共模)配合使用、变压器会饱和、并且从我的测量结果中、共模噪声抗扰度比 L-C 更差

我还没有测试一个功率扼流圈双线圈(为了在电感器之间实现更好的匹配=差分噪声转换不太常见)并将电缆屏蔽用作负导体(请参阅 https://www.ieee802.org/3/cg/public/Sept2017/stewart_01_0917.pdf 的第3页)

感谢您的建议、帮助等。