您好!

我将 DS90UB954-Q1用作解串器、用于 通过 Coaxia 配置供电。 滤波器电路 如图1所示。

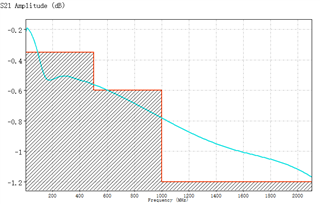

该滤波器电路仿真符合 FPD-Link 插入损耗要求、 如图1所示。

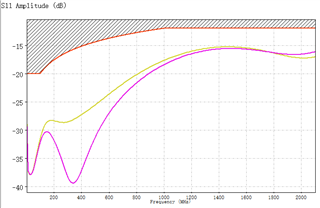

但是、在2.5D PCB 仿真中、它未达到标准、 请参阅图2。

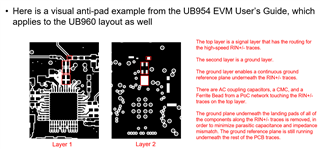

我的 Coaxia 供电布局如图3所示:

如何改善插入损耗?

期待获得指导!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我将 DS90UB954-Q1用作解串器、用于 通过 Coaxia 配置供电。 滤波器电路 如图1所示。

该滤波器电路仿真符合 FPD-Link 插入损耗要求、 如图1所示。

但是、在2.5D PCB 仿真中、它未达到标准、 请参阅图2。

我的 Coaxia 供电布局如图3所示:

如何改善插入损耗?

期待获得指导!

张您好、

通常、插入损耗的一个主要因素是高速布线上的阻抗不匹配。 我们的 FPD-Link 器件要求954的 RIN+和 RIN-布线具有严格控制的50欧姆(+/-10%)单端阻抗。 为了实现此阻抗、必须在整个高速 PCB 布线下方有一个连续的接地层。 在高速路径上的任何组件的焊盘下方也必须有接地切口、例如交流耦合电容器、ESD 二极管和接触 RIN+走线的 PoC 组件。 这是因为焊盘宽度增加会增加 PCB 布线的阻抗、并可能导致阻抗不匹配超出允许的50欧姆(+/-10%)范围。 着陆垫之间的寄生电容也会增加、这将影响高速路径上传输的数据。

我们还建议采用多种布局准则、例如沿 RIN+布线布置 RIN-布线、如果在顶层/底层布线、则一直到连接器、以引入差分特性并最大限度降低 EMI/EMC。 有关 完整详细信息、请参阅954数据表中的第10.1节 PCB 布局指南。

您分享的图片太小、我无法详细查看。 如果您愿意、您可以提供布局文件并请求布局审阅。 但请记住、这是一个公共论坛、因此您可能需要单独向我发送消息。

我还注意到、我无法识别您在共享的第一张图片中使用的 PoC 网络。 如果客户在其设计中使用自定义 PoC 网络、则他们将负责验证该网络不会对其系统产生重大影响。 954数据表中推荐了 PoC 网络、经验证可在4G 和2G 正向通道线路速率下工作、并支持通过 PoC 网络消耗高达150mA 的电流。

最棒的

Justin Phan

感谢您的回答!

我们的 PoC 网络需要在300mA 的电流下工作、因此954数据表中推荐的 PoC 网络不合适。

我们的回波损耗仿真符合要求、插入损耗也在高频下传递、即1GHz 到2.1GHz。 我认为这些结果可以证明阻抗没有严重失配。 但 奇怪 的是、插入损耗在低频(25MHz 至1GHz)下失败。

我现在怀疑 PoC 设计是错误的。 这是一种可能性。 另一种可能是布局中的某个位置发生意外谐振。

在这种情况下、S11通过、S21在低频下失败、您有什么建议吗?

张您好、

您是否曾尝试移除接触 RIN+跟踪的 PoC 组件、然后再次运行仿真、以查看 PoC 网络对 S 参数值的影响?

此外、我建议对阻抗结果进行仿真、并确认 RIN+走线实际上在50欧姆(+/-10%)以内、甚至构建测试板并使用 TDR 和 VNA 测量阻抗和 S 参数。

我可以提供的另一项功能是执行布局审阅、我可以在其中更详细地查看您的布局并在~1-2周内提供评论。 但这需要您提供 PCB 中每层的更详细图片或提供 PCB 项目的设计文件。 如果这是您想要寻求的、则您可以单独向我发送这些文件的私人邮件、因为这是一个公共论坛。

最棒的

Justin Phan