Other Parts Discussed in Thread: SN65LV1224B, SN65LV1023A

主题中讨论的其他器件: SN65LV1023A

您好!

我一直在使用 MAX9205/MAX9206和 SN65LV1023A/SN65LV1224B 串行器/解串器 LVDS 对进行大量测试。 使用 Maxim Integrated CHIPS 进行测试时、我成功地获得了稳定的锁定信号(超过10小时、而 MAX9206!LOCK 信号变为逻辑高电平)、具有16.666、20和25 MHz 的不同 TCLK/REFCLK 频率。 我一直在使用 MAX9205EVKIT 评估板进行测试。 最近、我将引脚兼容的 SN65LV1023A 和 SN65LV1224B 交换到了 MAX9205EVKIT 上。 我希望能够利用 TI SN65LV1224B 提供的10MHz 的较低最小 PLL 频率。 TI 器件中的 PLL 似乎运行方式不同? 我的测试设置没有变化、但我遇到了位错误、!LOCK 信号即使在最低频率10MHz 时也会变为逻辑高电平。 当我将频率增加到11、12 13 MHz 等时,!lock 信号会变差 它在16.667 MHz 频率下不可用、我之前在 MAX9206上取得了很大的成功。

我是否错误地假设这些是引脚兼容的?

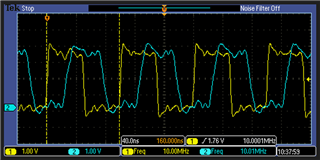

我将提供一个干净的 TCLK 和 REFCLK。 我使用的是10米长的 Cat5e。 在测试 MAX9205/9206对时、这两个变量是相同的。 所附的是一些示波器图像。 一个显示了在 TCLK 信号上触发时的无限持久性。 您可以看到、TCLK 的抖动很小、LVDS 差分数据的相位关系是恒定的、抖动也很小。 实心蓝色条表示 TCLK 和 REFCLK 之间的相位关系不是恒定的。 它们位于不同步的独立 PCB 上、但这是可以的、我能够使用采用相同设置的 MAX9205/9206对成功发送数据。 SN65LV1224B 上的 PLL 未被锁定到此串行数据、我感到很惊讶。 第二个图像触发!lock 信号变为逻辑高电平。

提前感谢您抽出宝贵的时间提供宝贵的建议。 此致、