主题中讨论的其他器件: TDP142、 SN65DP141

大家好、团队、

我的客户正在使用 SN75DP130 DP 转接驱动器从 FPGA 驱动 DisplayPort 输出。 它们不希望在灌电流中实现 DP130、而是希望在拉电流侧(电缆之前)实现 DP130。 我的问题是、由于 DP130将与接收器一起进行链路链路链路链路、源器件应如何处理链路链路趋势?

此致、

Renan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、团队、

我的客户正在使用 SN75DP130 DP 转接驱动器从 FPGA 驱动 DisplayPort 输出。 它们不希望在灌电流中实现 DP130、而是希望在拉电流侧(电缆之前)实现 DP130。 我的问题是、由于 DP130将与接收器一起进行链路链路链路链路、源器件应如何处理链路链路趋势?

此致、

Renan

尊敬的 David:

请参阅以下我的客户的回复:

感谢本主题、本视频重点介绍了 DP130作为线性转接驱动器的替代方案、无需链路训练。 我理解这一点。

但我想继续关注我当前使用 DP130的实施方案。

是的、我的源设备符合 DisplayPort 标准、如果接收设备直接连接到它、它将能够进行链路训练。

但我的问题是:在我的例子中、符合 DP 标准的源进行链路训练、它如何与同时进行链路训练的 DP130进行交互。 它是否透明、或者我是否应调整源固件以绕过链接培训的某些部分?

此致、

Renan

Renan

DP130 “监测”AUX 通道并接收来自链路训练过程的输入。 在这种情况下、它将根据灌电流请求调整 VOD 和预加重电平。 基于该输入、DP130在通道中增加了升压功能并自动调节其 EQ。 但 DP 源端和 DP130之间没有关于链路训练信息的通信。

当我尝试解释使用 DP130限幅转接驱动器时的潜在缺陷时、请参阅随附的幻灯片。 在这种情况下、它们可以关闭 DP 拉电流链路训练、并手动调整 DP 拉电流 VOD 和预加重电平以补偿 DP 拉电流和 DP130之间的通道、并让 DP130处理 DP130和灌电流之间通道的链路训练、 也可以使用线性转接驱动器。

e2e.ti.com/.../Limited_5F00_Redriver_5F00_Link_5F00_Training_5F00_Limitation.pptx

谢谢

David

尊敬的 David:

请参阅以下我的客户回复:

感谢您提供满足我期望的信息。

现在、我了解 DP130是如何交互的、我的理解是侦听 AUX 会使源软件透明地执行此过程。 在我的实施中、我在源端拆分了收发器 VOD/前置放大器的重新配置、因为它是在 DP130和接收端之间完成的。

然后、我将调整源和 DP130之间的链路、并以硬编码的方式应用 VOD/前置放大器参数、因为 DP130与源位于同一个板中、因此 RE 在一个板和另一个板之间没有差异。

还感谢文章显示了连接2个转接驱动器(一个位于拉电流端、另一个位于灌电流端)的长电缆的潜在缺陷。 这是一个有趣的知识。感谢高光。

我在均衡器侧还有另一个问题(在来自源极的输入端)。 如何调整参数? 它是从 DP130自动生成的、还是我们应该调节并写入 I2C 寄存器?

此致、

Renan

尊敬的 David:

请我的客户在下面回复:

我的问题更多地是如何确定 EQ 参数集最适合我的硬件。 如何找到最佳设置。

我可以从我的 IP 供应商那里获得一个示例、他的卡上还使用了 DP130、他们为我提供了将值写入 DP130 I2C 寄存器的函数。 请在下面找到该例程、并告诉我您的意见:

//在 bitec 灌电流主链路输入端插入 SN75DP130

//(在 Beitec 子板上)

//根据您的设计要求设置 SN75DP130均衡器

{

unsigned char data[32];

BITE_i2c_init (OC_I2C_MASTER_0_BASE);

BITE_i2c_write (0x58、0x01、0x03);

BITE_i2c_write (0x58、0x03、0x18);//禁用降噪

BITEC_i2c_write (0x58、0x05、0xD2);//force EQ for lane 0、pre-emphh 0_1、EQ_I2C_enable

BITEC_i2c_write (0x58、0x06、0x10);//force EQ for lane 0、pre-emphh 2_3

BITEC_i2c_write (0x58、0x07、0x52);//强制 EQ 用于通道1、pre-emph0_1

BITE_i2c_write (0x58、0x08、0x10);// for

此致、

Renan

Renan

它们是否有用于测量 DP130输出端原始波形或眼图的示波器? 它们可以根据 原始波形或眼图的信号质量来调整 DP130 EQ。

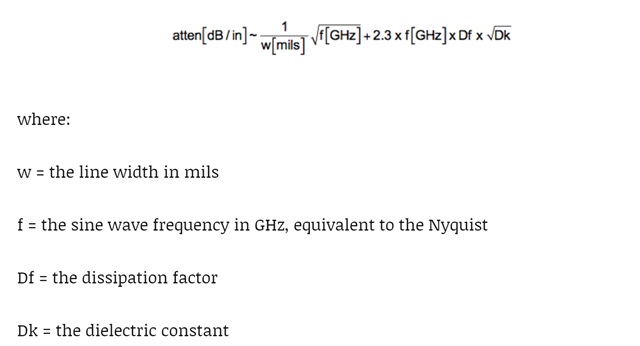

如果没有、则可以使用以下公式估算 DP 源和 DP130之间的 PCB 迹线损耗、

因此、当数据速率为5.4Gbps (2.7GHz 奈奎斯特频率)、布线宽度为5mil、DF 为0.02、DK 为4.3)时、

=SQRT (2.7)/5+2.3 * 2.7 * 0.02 * SQRT (4.3)= 0.586dB/in

假设采用6in 迹线、则估算的 PCB 迹线损耗为3.52dB。

通过估算3.52dB 的 PCB 布线损耗、您可以将 DP130 EQ 设置为大致匹配该值。

谢谢

David