主题中讨论的其他器件:DP83826EVM

Srinivas (希望这对您有所帮助)、

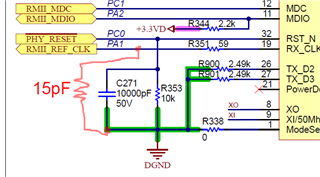

我们将根据 TI 的建议以及我们对上一个线程中的 DP83826EVM 进行的一系列测试、不断改变我们的设计、以使用 DP83826 PHY。

随附了更新后的设计、以 DP83826取代了 LAN8742A。 如前文所述、我们期待您在开始下一次构建之前对设计提出意见。

希望你们做得好-期待您能尽快收到您的回复。

小心-邓肯

e2e.ti.com/.../DP83826-PHY-Review-Copy-_2D00_-Schematic_5F00_10101.B_5F00_2021_2D00_07_2D00_20.pdf