大家好、

我在一条 RS485总线上使用 SN65HVD72。

在总线的一侧(在器件上)

当改变 NRE 引脚(从高到低以及从低到高)时、

Rx 引脚改变(低电平:持续时间500ns)

它应该处于一个很高的状态!

问题是什么?

谢谢、此致、

Stjepan

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

在我的应用中、我必须将 SN65HVD72DR 的工作模式从 TX 更改为 RX、反之亦然。

SN65HVD72DR 的原理图如下所示:

/RE 和 DE 引脚由我的微控制器(MCU)控制。

MCU 的供电电压为2.5V。 SN65HVD72DR 的供电电压为3.3V。

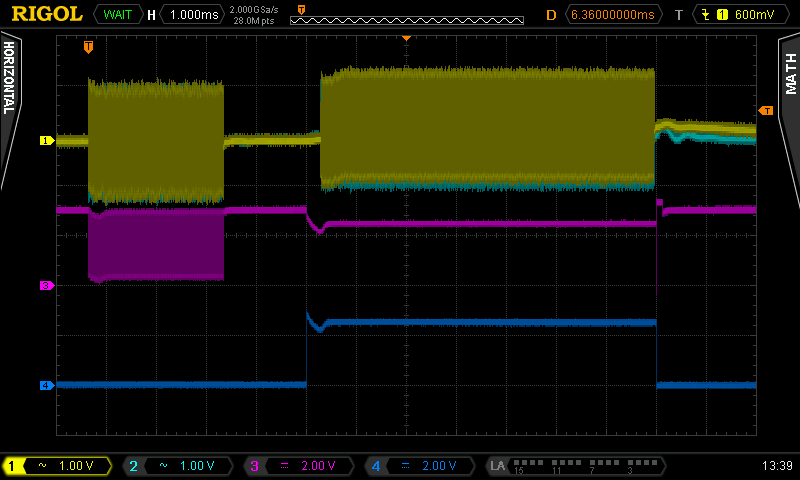

下面是问题的示波器图像:

示波器图像显示折页:

SN65HVD72DR 的 CH1 - B 线路(SN65HVD72DR 的引脚7)

CH2 - SN65HVD72DR 的一条线路(SN65HVD72DR 的引脚6)

CH3 - SN65HVD72DR 的 R 线路(SN65HVD72DR 的引脚1)

SN65HVD72DR 的通道4 -/RE 线路(SN65HVD72DR 的引脚2)

如您所见、图像右侧的 CH3 (R LINE)中存在干扰。

图像不显示 DE 线路(SN65HVD72DR 的引脚3)。 在我将/re 从高电平更改为低电平时、将 DE 线路从低电平更改为高电平。 但 DE 和/RE 不会同时切换。

当我将 SN65HVD72DR 的/RE 引脚从高电平更改为低电平时、就会产生这种毛刺脉冲。

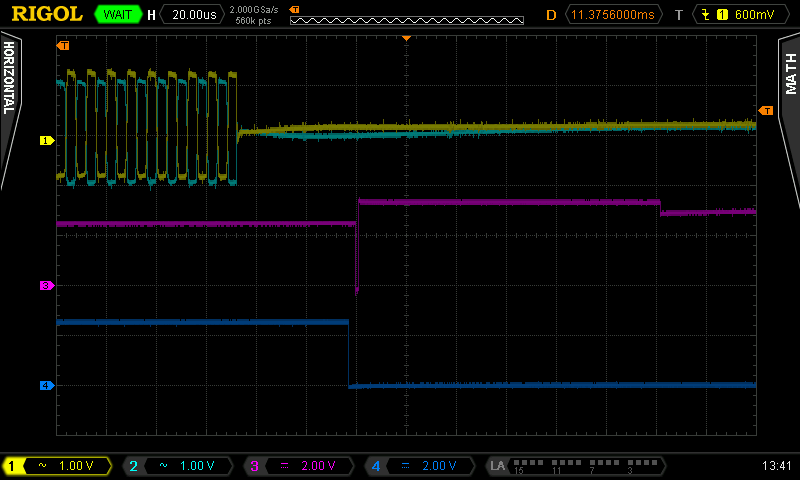

放大的毛刺脉冲如下所示:

是否有人建议为什么会发生这种情况?

谢谢!

感谢您提供的信息、以帮助我了解问题。 如果您在示波器上绘制差分总线电压(A-B)、我想您会看到该电压在短时间内接近或低于-200mV (SN65HVD72接收器的阈值 Vit-)、这使得接收器产生低电平(毛刺脉冲)。

由于 DE 和 REB 是单独控制的、因此您可以延迟 REB 的导通时间以等待总线电压稳定。 另一种可能的解决方案是在 A 和 B 之间添加终端电阻器、以帮助总线稳定并获得更好的信号完整性。