大家好、

我们是否有更新的 BDSL 文件? 客户正在使用 此线程中的 BDSL 文件 、但 当他们尝试在链中使用此器件设置和测试 JTAG 链时、链会由于与指令寄存器长度不一致而失败。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们是否有更新的 BDSL 文件? 客户正在使用 此线程中的 BDSL 文件 、但 当他们尝试在链中使用此器件设置和测试 JTAG 链时、链会由于与指令寄存器长度不一致而失败。

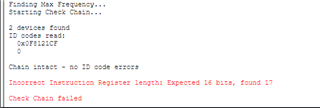

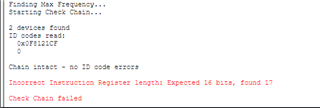

当使用 XJTAG 进行 JTAG 链设置和控制时、会遇到该错误。 链中有2个器件、即以太网 PHY 和 Polarfire FPGA。 他们尝试从 链中移除 phy、JTAG 链工作正常、并得出结论认为 BDSL 存在问题。

我希望你能提供帮助。

谢谢你。

此致、

Marvin

您好、Gerome、

感谢您的更新。 在等待期间、您能帮助回答以下后续问题吗?

如果 nRESET (引脚43)保持低电平、PHY 是否能够执行 JTAG 边界扫描操作? 与目前一样、我们的 FPGA 与 PHY 位于同一链中、负责将器件从复位状态中驱动出来。

此外、如果引导配置未设置为用于边界扫描模式的 JTAG、器件是否会在链中做出响应?"

谢谢你。

此致、

Marvin

您好、Gerome、

谢谢!

客户已进行了更新:

"因此、我们在圈中进行了一些测试、并测量了返回 TDO 线路上提供的数据

如果您查看捕获的值

0x96a5a569

红外捕获0b00000000000000000001001011010100101101011010010001000000000

IR 预期0b 100101101010010110100101101001

您可以看到我们的时钟值是在哪里产生的。

FPGA 的 IR 寄存器应为8位宽、并将01作为返回 LSB、这一切看起来都正常。

然而、PHY 的 IR 也应该为8位宽、并且应该捕捉一个0b11011101的值。

您可以看到返回的数据有9位、所有这些位的值都为0。"

此致、

Marvin

您好、Gerome、

您是否还会回答以下问题?

[引用 userid="510099" URL"~/support/interface-group/interface/f/interface-forum/1133122/dp83869hm-updated-bdsl-file/4208488 #4208488]n 如果 nRESET (引脚43)保持低电平、PHY 是否能够执行 JTAG 边界扫描操作? 与目前一样、我们的 FPGA 与 PHY 位于同一链中、负责将器件从复位状态中驱动出来。谢谢你。

此致、

Marvin