您好!

我有 几个7.2Gbps 聚合数据流 在 TLK10022 HSTX_A/B_P/N 输出端发出、并由 Xilinx FPGA 在 MGTHRXP/N 输入端接收。

关于 FPGA RXDATA CLK、一种选择是使用 FPGA 内部 RXDATA 中恢复的 CLK、另一种选择是将 RXCLK 作为 REF CLK 馈送到 FPGA、以获得更好的 RX CLK 质量、尤其是从抖动备用点。

我使用单个 REF CLK 来驱动 TLK10022 A/B 通道、并且仅使用 TLK10022的聚合器部分(TX 侧)。

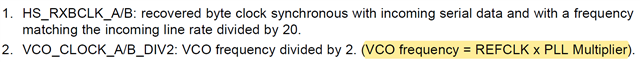

TLK10022具有 CLKOUT_A/B_P/N 输出、根据数据表、它可以由 HS_RXBCLK_A/B (在我的情况下未使用)或 VCO_CLK_A/B_DIV2驱动。

Q1) VCO_CLK_A/B_DIV2及其与 7.2Gbps HSTXA/B_P/N 输出数据流的关系、有关频率、CLK/数据之间的延迟等

Q2)由于我不使用 HSRX_A/B_P/N RX 端、TI 对于未使用的 RX CML 输入和整个 RX 部分有何建议?

此致、

请