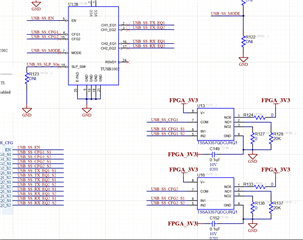

Other Parts Discussed in Thread: TUSB1002

请解释 CANGIG 引脚内部上拉/下拉的行为以及这些引脚采样的时序。

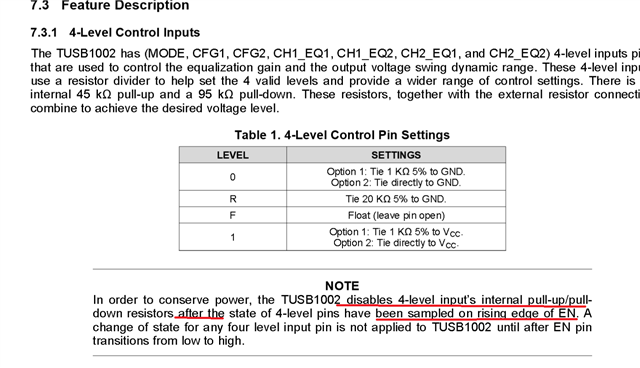

数据表中的以下语句似乎意味着当 EN 引脚为低电平时、CONFIG 引脚上的内部拉电阻将处于活动状态、并且在 EN 转换为低电平后会禁用这些引脚

为了节省功耗,TUSB1002 在 EN 上升沿对4电平引脚的状态进行采样后禁用4电平输入的内部上拉/下拉电阻器。 在 EN 引脚 从低电平转换为高电平之前、任何四电平输入引脚的状态变化都不会应用于 USB1002。

但是、这不是我在电路板上看到的结果。 打开电源后、在 CFG 引脚悬空的情况下、即使这些引脚处于 F 和 R 状态、我也会测量这些引脚上的零伏电压。

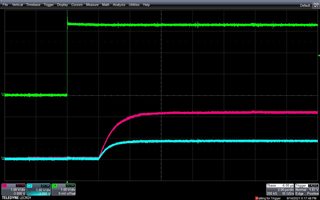

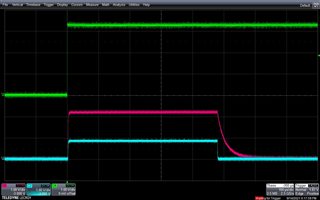

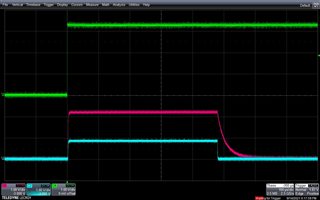

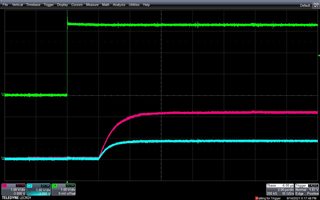

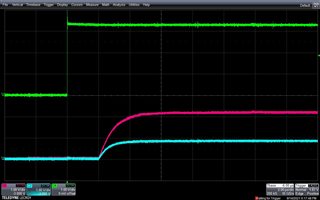

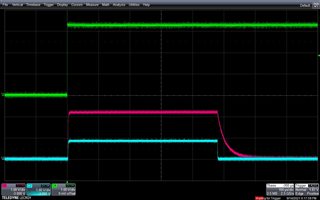

我在示波器上看到的是、在 EN 上升沿之后、拉动看起来大约为10uS、然后在大约470uS 之后关闭。

我在 DS 中没有看到任何东西暗示内部拉电阻几乎总是关闭的事实,当 EN 变为高电平时,内部拉电阻器被打开,被采样,然后关闭。

为了使事情更加混乱、数据表中的图2表明、在 EN 变为高电平后、CFG_HD = 500us 时、CFG 引脚值需要保持稳定。 但芯片本身会在不到500us 的时间内关闭内部拉电流。 tcfg_HD 的含义可能 不同于"在时钟之后保留输入上的数据以实现保持时间"?

这些 CFG 引脚何时精确采样? 当 EN 变为高电平时、很明显拉电流甚至不打开时、我无法看到如何在 EN 的上升沿对其进行采样。

下面的波形是否与我在正常运行中应该看到的波形类似?

绿色轨迹线= EN

洋红色、青色迹线= CFG 引脚(一个处于 F 状态、另一个处于 R 状态)