主题中讨论的其他器件:SN65DSI84、 LMK61E0M

您好!

我们有以下配置:

MIPI DSI => DS90UB941 => 1单端 FPD 链接=> DS90UB948 => LVDS 屏幕(60fps 时为800x1200)

PCLK = 72MHz

当串行器使用外部时钟(DS90UB941)时,LVDS 上像素时钟的时序容差是多少?

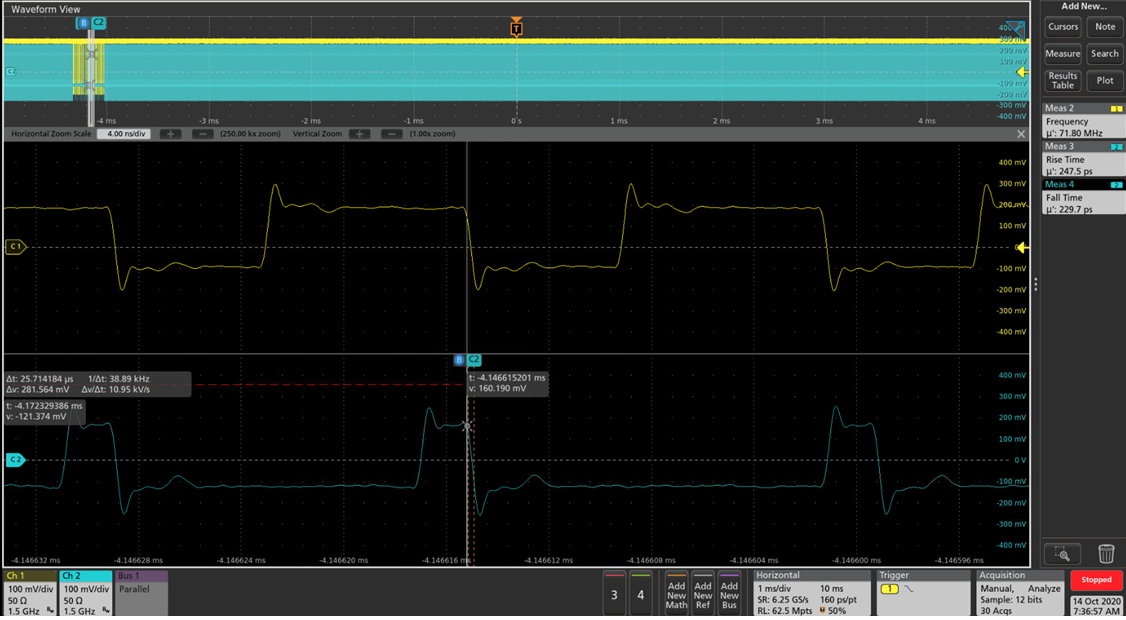

我进行了一些测量、并具有以下特性(在像素时钟中):

水平前沿/水平同步/水平后沿/数据

56/24 / 24 / 799 = 903

55 / 24 / 24 / 800 = 903

58 / 24 / 23 / 800 = 905

当使用 DS90UB941的 MIPI 时钟进行相同测量时、我可以根据 MIPI 配置实现稳定的计时:

72 / 24 / 24 / 800 = 920

为什么前沿有不同的时序、为什么外部时钟计时不稳定?

MIPI 时钟和外部时钟域之间的重定时吗?

是否有可能改进它?

我们还具有与 SN65DSI84 (MIPI 转 LVDS 桥接器)相同的行为(屏幕闪烁)。

谢谢、

此致、

亚历山大