Other Parts Discussed in Thread: SN65MLVD206

大家好、团队、

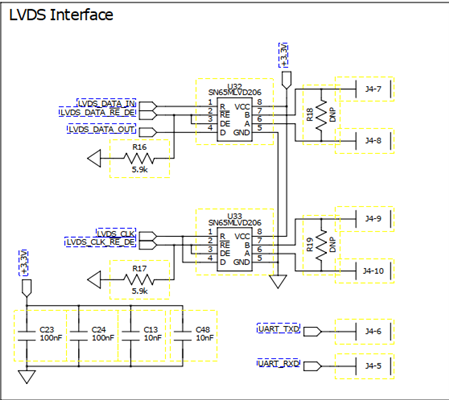

我的客户正在使用 SN65MLVD206 进行 SPI 时钟发送/接收。 RE 和 DE 引脚通过导线(短接在一起)连接到 uC 的 GPIO。 UC 通过拉高或拉低来控制这些引脚的状态。 使用此方案是否会出现问题? 在这种情况下、uC 可以是 SPI 主器件或从器件、因此需要双向时钟信号。

与上述情况类似、出于相同的原因、引脚 R 和 D 通过导线连接到同一器件。 可以这样使用吗?

此致、

Renan