VDD 引脚3、8、15、25、30 -通过去耦电容0.1uF 连接到3.3V 电源。

EQ0 - EQ3引脚11、12、39、40 -接地。

PE0 - PE3引脚18、19、20、31 -接地。

PWDN#引脚38 -连接至3.3V 电源、无任何上拉电阻。

PWDN0#- PWDN3#引脚32、33、34、35连接到3.3V 电源、而不会出现任何上拉。

LOS3#- LOS3#引脚13、14、36、37 -未连接、因为在我们的案例中不需要输出确认功能。

IN0 - IN4 -所有 LVDS 输入。

OUT0 - OUT4 -所有 LVDS 输出。

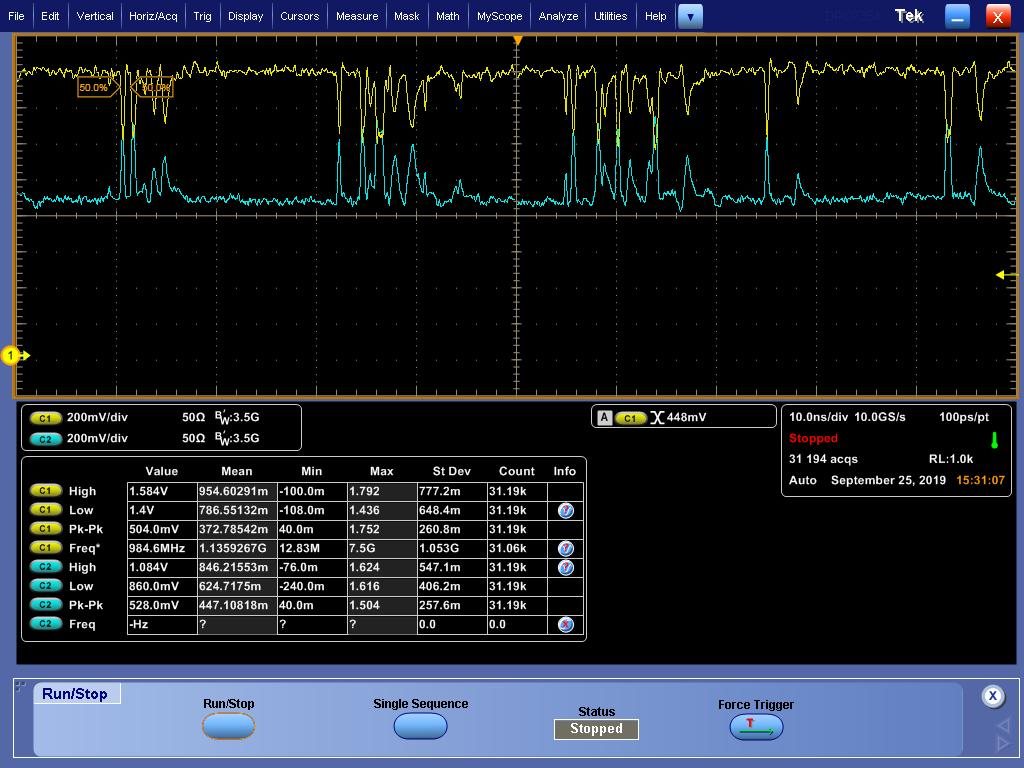

我们观察到、如果所有 IN0 - IN4 LVDS 输入全部为0V (无信号)、OUT0 - OUT4输出通道将具有如下行为:

a.) OUT0+ 1.3V 平坦、OUT0- 1.1V 平坦。

b) OUT1+和 OUT1-均为1.2V 平坦电压。

c.) OUT2+ 1.1V FLAT、OUT2- 1.3V FLAT (与项目 a 相比极性反转)。

d.) OUT3+ 1.5V 平缓电压、OUT3- 0.9V 平缓电压(与项目 a 相比、峰峰值更大)。

为什么4个输出通道的行为会彼此不同?

我们尝试将上述4个条件设置为这次连接到 IN0 - IN4、观察结果如下:

a.)如果 IN+和 IN-均为1.2V 平坦(共模)、则该特定通道上的 OUT+和 OUT-肯定会有信号翻转。

b.)如果有任何 IN+和 IN-采用 LVDS 差分形式、则该特定通道上的 OUT+和 OUT-将遵循输入。

c.)通道2将始终具有极性反转。

d.)所有通道的输出峰-峰值都将增加。 OUT+ 1.5V、OUT- 0.9V

为什么常见的1.2V 信号会导致信号翻转? 为什么通道2始终具有极性反转?