Other Parts Discussed in Thread: PCA9548A

尊敬的 E2E:

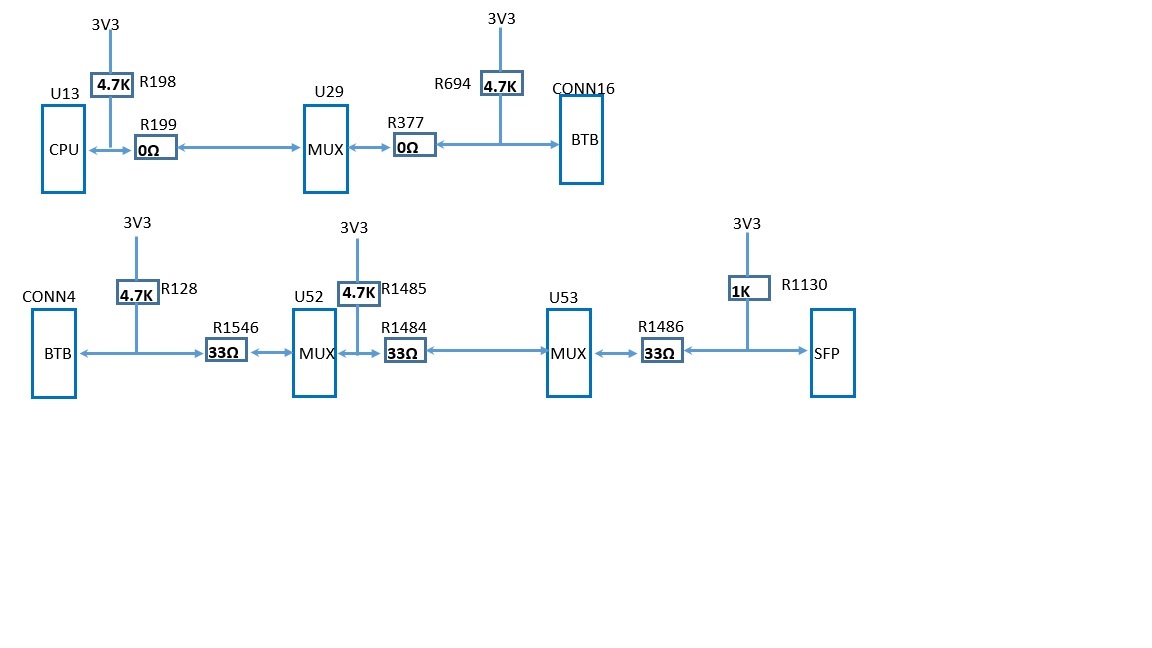

I2C 信号通过5个串联的 PCA9548A 作为级联在 CPU 和 SFP 收发器之间进行通信。

它们在从 CPU 到 SFP 收发器的每个网络上都放置了上拉电路。

SFP 收发器的规格要求最小上拉电阻。

我们的问题是、当我们站在 SFP 收发器的位置时、有效的上拉电阻是什么?

我认为有效的上拉电阻器是将所有上拉电阻器从 CPU 并联到 SFP。 我是对的吗?

另一个问题是、我看到 PCA9548A 的内部拓扑是无源 FET。 如果是、我们为什么仍需要在输入和输出侧放置上拉高电阻器?

BR、

Jason