您好!

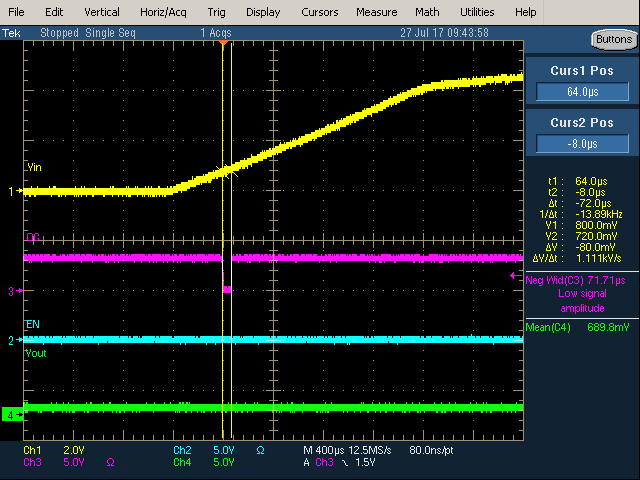

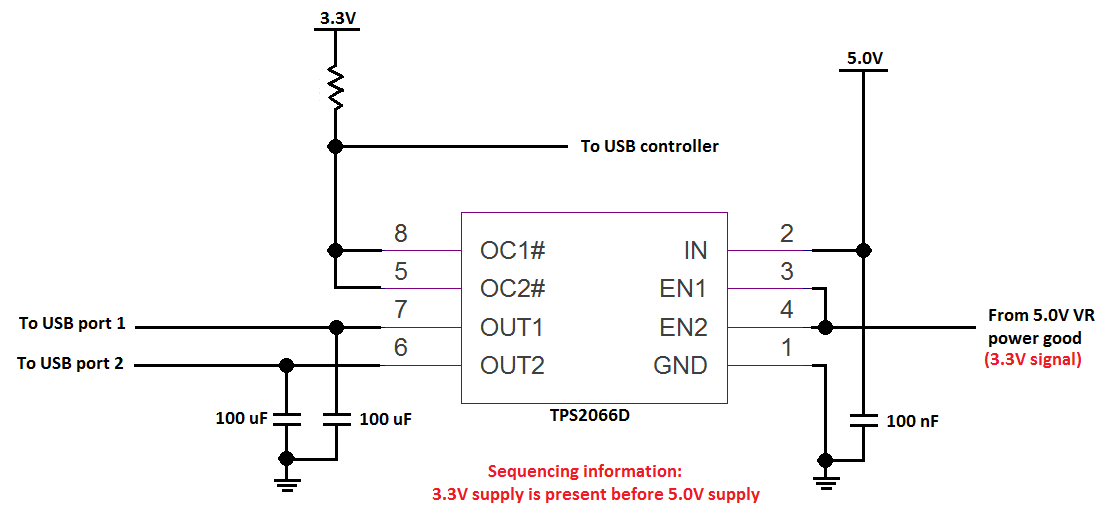

我们目前使用 TPS2066D 作为 USB 端口的负载开关。 Y 在 VIN 引脚斜升时、在 VIN 仍然很低(~ 0.72V)的情况下、OC 引脚上会出现毛刺脉冲。 此干扰有时会被 USB 控制器解释为过流事件、并导致端口故障。 开关和控制器之间的线路上没有其他连接、因此该干扰必须由 TPS2066D 本身发出。

我想知道这是否是该组件的预期行为。 我知道有一个 UVLO 功能可以在 VIN 电源低于特定范围时防止故障、但在我们的情况下、该功能似乎不能防止 OC 引脚发生毛刺脉冲。

请参阅随附的示波器捕获。

谢谢你。

Cedrick