请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN65LVDT388A 您好!

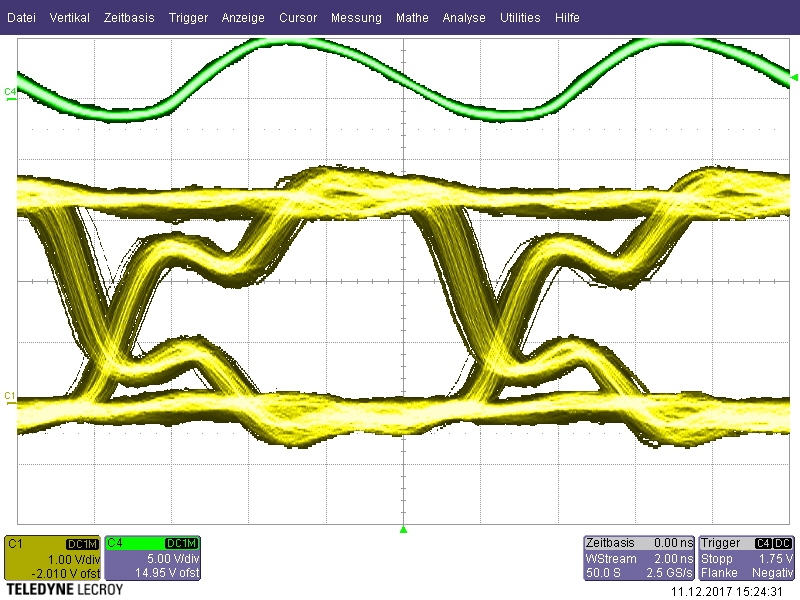

我们有一个应用、希望通过 LVDS 技术以高达100Mbit/s 的速度传输数据。 因此、我们选择了 SN65LVDT388A 器件。 我们使用将引脚35 (A1Y)连接到 Xilinx Artix-7 (AC701板)的测试板测试了@ 100Mbit/s 的信号完整性 不幸的是、上升沿和下降沿 看起来并不是很有希望。 请参阅随附的眼图 CH1 (黄色信号)。 当我使 SN65LVDT388A 的输出保持开路时、信号看起来完美。 Xilinx Artix-7的输入引脚配置为 LVTTL 为3.3V。

SN65LVDT388A 和 FPGA 之间的距离约为8英寸。 是否有任何想法、问题可能出在哪? 反射是否可能会导致这样的信号?

谢谢、此致、

Patrick