工具/软件:Linux

我们的客户遇到紧急问题、需要帮助!

他们的公司有一个 RSB-468项目和15件产品、并发现6件 LAN 上/下故障。 具体描述为:

禁用 LAN、然后启用 LAN,LAN 将不起作用、必须多次重新启动或启用、然后功能正常。

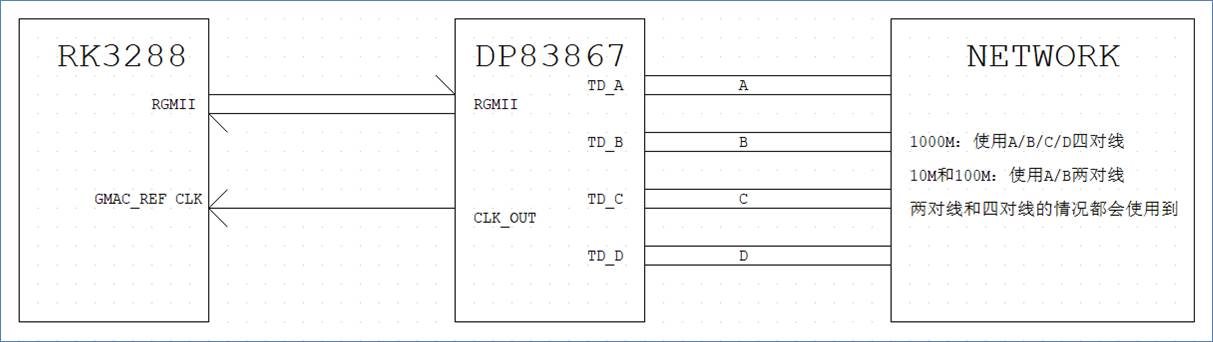

(__LW_AT__)TI LAN PHY DP83867IRRGZT

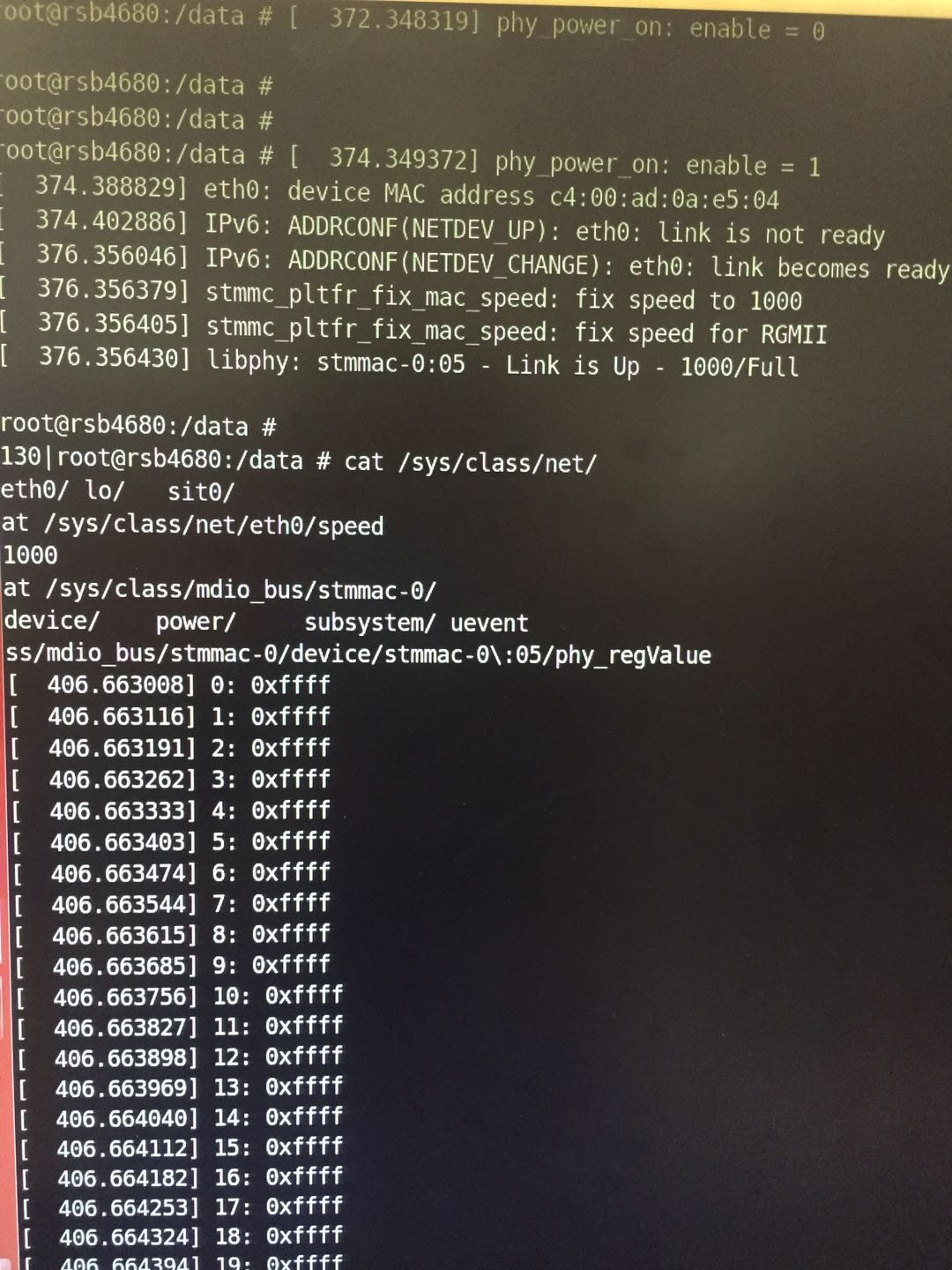

1.用户环境:android6.0 (kernel3.10),如果配置 eth0 down/up,则将随机解决该问题。

2.他们的工程师配置了类似这个 μ:的寄存器

//地址掩码值

0x0014 0x200 0x200

0x0018 0x0x0x65b

0x001e 0x200 0x200

0x0032 0x3 0x3

0x0086 0xff 0x80

0x0170 0x1f00 0x0000