Other Parts Discussed in Thread: DS32EL0124, DS32EL0421

主题中讨论的其他器件: DS32EL0421

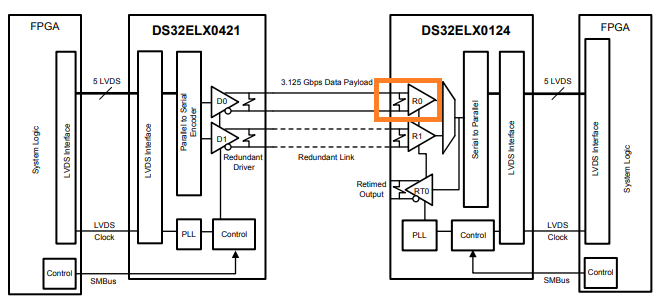

我们正在开发一个 DAQ 模块、该模块将使用其中的32个芯片对32个2.5Gbps 数据流进行反序列化。 数据信号来自不遵循任何传统协议的专有传感器。 我们之所以选择此芯片、是因为它接受直流耦合信号、并且能够禁用8b/10b、直流平衡解码器。

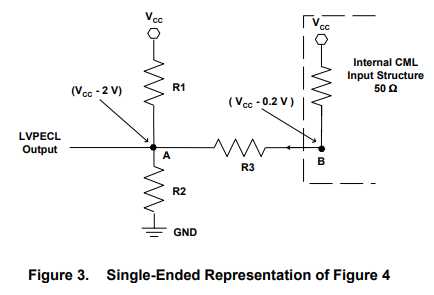

我们系统中的驱动器是3.3V LVPECL、因此我们需要确定如何将其与 DS32EL0124的 CML 接收器耦合。

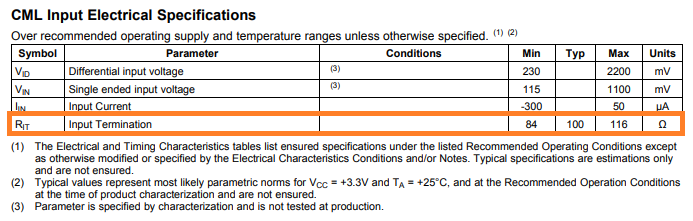

数据表仅提到芯片在内部是"自偏置"的。 这真的不足以确定如何最好地将 LVPECL 源与 DS32EL0124耦合。 实际上、确定如何将其与 CML 源结合使用也是不够的。 我知道 DS32EL0124和 DS32EL0421通常设计为在不使用任何外部偏置组件的情况下一起使用。

是否有一些内部上拉机制? 您能描述一下此芯片的 CML 接收器的输入结构吗?

谢谢