我有一位客户目前正在评估 RS-232应用的 SN75C185。

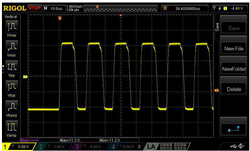

他们观察到一个位为高电平或低电平的时间长度存在差异、如所附图像所示。

波形是在 RS-232驱动器 IC 的输出端测得的。

-波特率= 115200bps

-周期计算为8.7µs μ s、高电平时间为~1.2µs μ s 过长、而低电平时间为~1.2µs μ s 过短

从 DS 中、tPLH (L->H 传播延迟)的典型值为1.2µs μ s、而 tPHL (H->L 传播延迟)的典型值为2.5µs μ s。

因此、"高电平"时间比"低电平"时间更长...

但是、从 RS-232-C 标准的角度来看、这种行为(观察到的 H/L 时间长度变化与波特率之间的关系)是否可以接受?