Other Parts Discussed in Thread: SN65LVDS31

您好!

我们使用该器件来驱动未供电的 FPGA、并尝试找出影响。

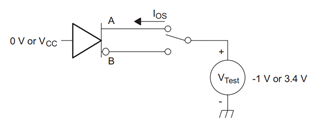

从数据表中可以看出、100 Ω 电阻器上的驱动电流通常为3.4mA、其中一个输出引脚(neg 或 pos)的短路电流为4至24mA。

在我们的系统中、LVDS 输出将通过电缆、然后正向偏置 FPGA 中的功率钳位二极管。 由于存在一些负载、我们是否可以假设电流将保持在3.4mA 左右、或者电流是否会增大? 此器件是否有电流与负载间的关系图会显示此情况? 24mA 最大短路电流是如何产生的?

此外、如果没有负载、LVDS 输出高侧将为3.3V?

谢谢、

Todd