Other Parts Discussed in Thread: TCA9548A, TCA9511A

主题中讨论的其他器件: TCA9511A

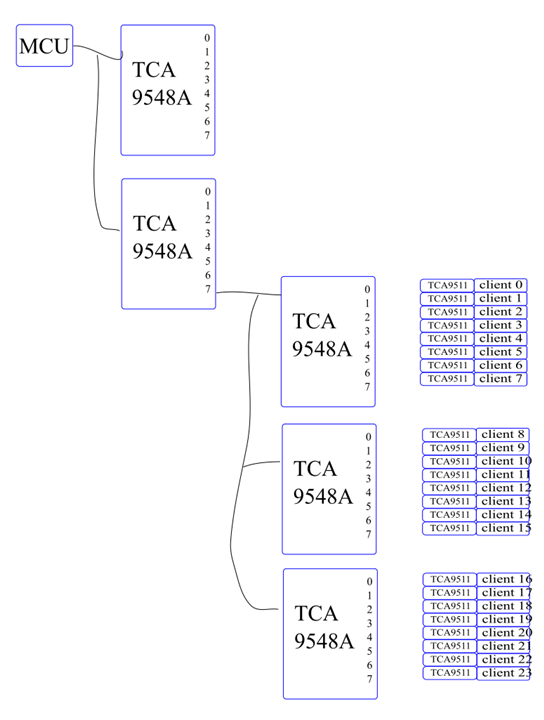

前两个 TCA9548A 来自评估板、我想使用其中一个 I2C 通道、并进一步扇出至24个插槽。 对于每个插槽、我希望使用一个或多个 SI18IS606将 I2C 转换为 SPI、也可以使用 EEPROM。

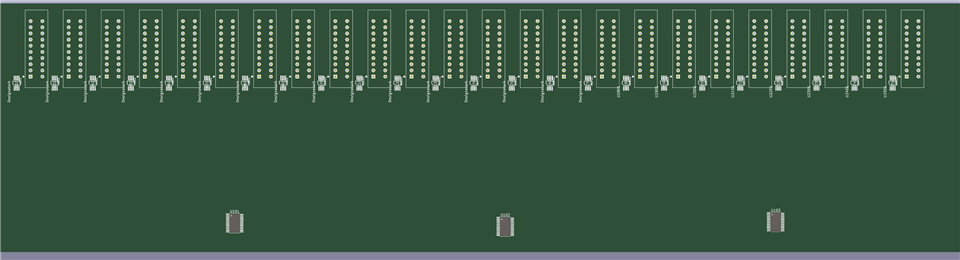

电路板尺寸为~300x100mm

这种做法是否可行?

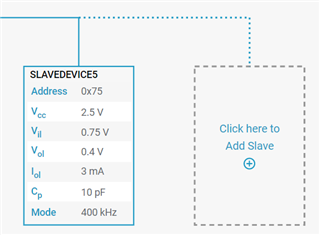

在 TCA9548A 之前、我是否需要 TCA9511? 如果3个 TCA9548A 的每个电流约为100mm?

如何估算这里的电容?