https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1225821/sn65dp141-design-help

器件型号:SN65DP141您好!

你好。

我的案例:笔记本 -> DisplayBoard 电缆 -> SN65DP141作为输入缓冲器 IC、即引脚 IN0_P、IN0_N…… IN3_P、IN3_N -> FPGA (i.e、SN65DP141的线路 OUT0_P、OUT0_N…… OUT3_P、OUT3_N 已连接至 FPGA)。

接下来是 GPIO 配置模式(不是 I2C!)。

我的问题:

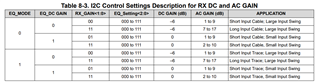

1.引脚 EQ_Mode/ADD2 (引脚35)。 我应该选择什么? (因为我有一条3m 的 DP 电缆从笔记本电脑连接到 SN65DP141)? 还是迹线(因为我从 SN65DP141到 FPGA 有短的 PCB 迹线)?

2.引脚 EQ0/ADD0、EQ1/ADD1、RX_GAIN。 如何选择 EQ_AC_GAIN ? 在本例中、EQ_DC_GAIN = 1 (或0dB)。

请告知。 非常感谢。

此致、

雷·文森特