大家好、团队成员。

我们的客户向我们询问了 DS250DF230配备不稳定 CDR 锁定的情况。

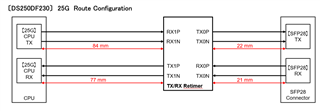

图像上部的方框图(默认)是运行中使用的配置。

DS250DF230的交叉点被启用并路由至下方。

CPU (LX2160A)--> DS250DF230 --> SFP28

SFP28 --> DS250DF230 --> CPU (LX2160A)

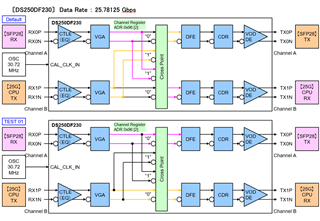

最下面一行(测试01)的框图是环回进行验证的配置。

DS250DF230的交叉点未进行切换、因此路线如下。

CPU (LX2160A)--> DS250DF230 --> CPU (LX2160A)

SFP28 --> DS250DF230 --> SFP28

在两种配置中、来自 CPU (LX2160A)的输入信号(RX1)的 CDR 锁定不稳定、因此底部一行中测试01中的配置经过验证。

使用 SigCon Architect 的 GUI 工具

数据速率:25.78125Gbps

DS250DF230的校准时钟引脚(CAL_CLK_IN)为30.72MHz。

从 CPU (LX2160A)检测到的输入信号(RX1)信号正常。

CPU (LX2160A)的输入信号(RX1)处于 CDR 锁定/解锁状态。

e2e.ti.com/.../25G_5F00_Retimer_5F00_setup_5F00_01.cfge2e.ti.com/.../25G_5F00_Retimer_5F00_setup_5F00_01.xlsx

附加的"25G_Retimer_setup_01.cfg"是从"SigCon Architect"保存的数据。

保存自"SigCon Architect"的数据

操作的设置和启动仅如下所示。

1"重置设备

2"适用于所有通道

3复位 CDR 所有通道

"25G_Retimer_setup_01.xlsx"中的"test_01"表对应"SigCon Architect"上的每个屏幕。

test_01_01.bmp CDR 未锁定(通道1蓝框)

test_01_01a.bmp CDR 已锁定(通道1蓝色帧)

CDR 锁定不稳定。

我想获得有关在哪里检查以及进行哪些设置以稳定 CDR 锁定的建议。

此 致、