大家好

我现在使用 TUSB1210。

时钟是 TUSB1210的输入。

如果连接到 FPGA、TUSB I/0如下所示。

另一种协议。

datain 是 FPGA 的输入。

现在 DIR 太长,甚至在 nxt 之前开始

如何解决此问题?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

好的。

1)如果 PHY 接收,RXError 如何解决它?

2)

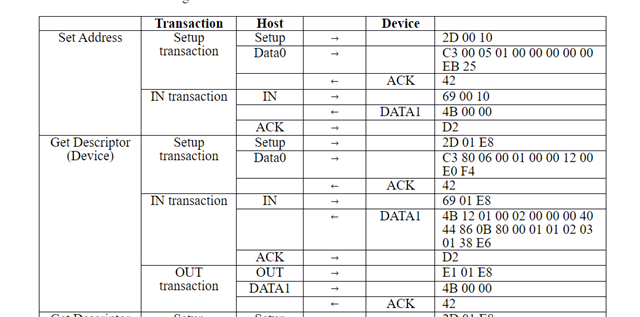

在枚举阶段、

我认为 PHY 的行为应是这样的、

是的,有时我可以看到。 但是、正如您 可以从 FPGA 看到我的波形、

2D0010 --> C38006000100004000DD94。

在本例中 DATA0为 C3 80 06…

但我认为应该是的

|

数据0 |

→μ A

|

|

C3 00 05 01 00 00 00 00 EB 25

|

在本例中、DATA0匹配。

我的问题是为什么 PHY 发送不同的 DATA0 ?

如何从 PHY 获得 DATA0?

从外部复位/时钟后,是否可以获得行为模式/描述?

复位后、PHY 应向 FPGA 发送 DIR/nxt。 但在本例中、我仍然不知道 PHY 会产生什么结果。

这样、我可以检查电路板设计... 但因为在我的情况下、u can DIR 始终为高电平(这意味着存在错误。。 但为什么呢?

哪个错误? 如何解决? 如何清除它?

我们的 FPGA 板具有 FPGA 芯片+ TUSB1210芯片。

在 FPGA 内部、有 USB 器件 RTL 代码。

所以设备( FPGA )<--> TUSB1210在一个单板.

器件输入信号与 U 共享

那么、对 TUSB1210的期望是什么?

我想它会尝试定期发送 DIR/nxt。 但我不知道 TUSB1210的输出。

以及 FPGA 的 TUSB1210中的预期信号