Other Parts Discussed in Thread: LMK1C1104, DP83869HM

主题中讨论的其他器件:LMK1C1104、

大家好!

请分享该指南以避免 EMI 问题。

时钟和其他信号所需的布线指南。

时钟输出引脚的端接要求。 如果它被连接到测试点,对于该引脚建议采用什么方法?

此致、

Harikrishnan T.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨、 Harikrishnan、

CLK_OUT 可直接连接到测试点。 您可以参阅 DP83869 EVM 用户指南 以获取参考原理图。

您试图遵循哪些 EMI/EMC 标准?

此致、

Melissa

嗨、 Harikrishnan、

我附上了布局指南列表。 请下载 Excel 文件并查看选项卡"通用布局指南"。

e2e.ti.com/.../3301.IndustrialPHY_5F00_Layout-Review-Checklist.xlsx

此致、

Melissa

尊敬的 Melissa:

感谢您的答复。 我还有一些问题

时钟架构:

在我的设计中、我有14个以太网接口。 10配置为1000BASE-T、4配置为100BASE-TX。

为此、我将与缓冲器共享公共时钟。

在我的设计中将 MEMS 振荡器 SiT8924BA 用作源、将 LMK1C1104用作缓冲器以将时钟共享给多个以太网 PHY。

尽管我的时钟架构是开放的、但我有两个想法。

1.各个 PHY 使用单独的振荡器

2.具有多个时钟缓冲器的单个振荡器

根据您的想法、哪一个是最好的想法? 如果您有任何其他想法、请告诉我。

对于这两个想法、关于时钟信号的布局和布线建议是什么。

请尽快解决我的问题。

此致、

Harikrishnan T.

尊敬的 Melissa:

我还有一个疑问。

我们是否可以将变压器放置在 PCB 的对侧(同一位置-顶层和底层)?

如果我们可以采取任何预防措施?

当我搜索以太网接口的布局指南时、我找到了 Pulse Electronics 的这份应用手册。

https://www.pulseelectronics.com/wp-content/uploads/2020/12/Pulse_Layout-Considerations-v7.pdf

根据本应用手册、PHY 和磁体之间应至少保持1英寸的距离。

我们是否必须遵循这项建议?

此致、

Harikrishnan T.

嗨、 Harikrishnan、

我们可以在 PCB 的两侧放置变压器(同一位置-顶层和底层)吗?

您是否要将其中一条布线布置到变压器的底部、然后再布置回顶部、以便两条布线都位于连接器的同一层?

。

当我搜索以太网接口的布局指南时、我找到了 Pulse Electronics 的这份应用手册。

https://www.pulseelectronics.com/wp-content/uploads/2020/12/Pulse_Layout-Considerations-v7.pdf

根据本应用手册、PHY 和磁体之间应至少保持1英寸的距离。

我们是否必须遵循这项建议?

[/报价]我们没有此要求。 每条 MDI 布线的总长度应小于2英寸或2000密耳。 如需更多信息、请参阅此应用手册: https://www.ti.com/lit/an/snla387/snla387.pdf?ts=1684776849250&ref_url=https%253A%252F%252Fwww.google.com%252F

此致、

Melissa

尊敬的 Melissa:

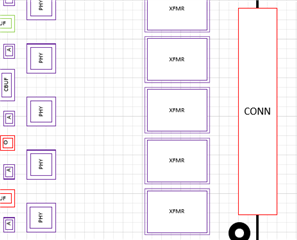

我将附加有关 PHY、变压器和连接器放置的假设。

连接器不是 RJ45。 以紫外颜色突出显示的 PHY 和变压器意味着它们放置在顶部和底部(相同位置)。

这是一个假设。 我们能像这样放置吗? 顶层 PHY 到顶层变压器底层也是如此。

我能不能这样的地方? 仅需要变压器放置方面的说明。

我要在布局中移动 PHY。

此致、

Harikrishnan T.

尊敬的 Melissa:

感谢您提供有关查询的信息。

我还有一个关于 SMI 接口(串行管理接口)的查询。

根据 IEEE 802.3-2022第22条第22.3.4节、MDC 和 MDIO 之间的延迟可以是0ns (最小值)至300ns (最大值)。

但在 DP83869HM 数据表第16页中、MDC 至 MDIO 延迟指的是0ns (最小值)至10ns (最大值)。

您能解释一下为什么与 IEEE 存在偏差吗? 上述时序在数据表中是否为10ns 误差?

此致、

Harikrishnan T.