Other Parts Discussed in Thread: TPD6E05U06

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1228102/tpd6e05u06-esd

器件型号:TPD6E05U06客户反馈使用此产品时无法满足 USB3.0要求。

我们是否具有相关的高速测试的 SI 模式?

或任何其他实验结果?

可以说服客户这不是我们的器件的问题。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TPD6E05U06

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1228102/tpd6e05u06-esd

器件型号:TPD6E05U06客户反馈使用此产品时无法满足 USB3.0要求。

我们是否具有相关的高速测试的 SI 模式?

或任何其他实验结果?

可以说服客户这不是我们的器件的问题。

尊敬的 Fabio:

提供的数据清楚地表明该器件可以支持比 USB3.0快1Gbps 的信号。 低速信号下的眼图会更好。

该数据是在 布线经过优化的电路板上获得的、以更大限度地减少干扰、如果电路板布局 在 USB 信号布线上具有高电容、则这可能会导致系统不合规。

插入图还显示了该器件 在~4Ghz (8Gbps)下的差分插入损耗为-3dB。

产品页面上提供了 IBIS 和 S 参数模型。

此致、

塞巴斯蒂安

客户关注的是阻抗、而不是图表。

1. S 模型下载的是模拟数据还是测量数据?

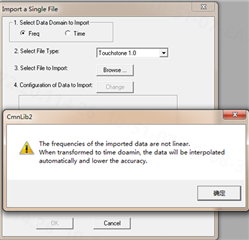

此数据域的横坐标是日志模型、而不是线性模型。 从此数据得出的阻抗不准确、但阻抗显然具有一个低点。

2.能否提供以下产品(PN:TPD6E05U06RVZR)中显示的线性 S 模型或阻抗测试结果(根据 USB3.0标准测试结果)?

现在、他们重点关注阻抗指标、而不是眼图或 IL。

3. USB3.0关联的阻抗规格为90+/-15欧姆。 因此、如果不能满足该要求、则可将该产品视为不合格。

尊敬的 Fabio:

我很抱歉我在商务旅行中迟到了回复。

1.使用模拟数据创建 S 参数模型

2.我们目前没有该器件的线性 S 模型或阻抗测试结果。

3.无法避免 ESD 二极管出现一定的阻抗不匹配、以保护频率在 GHz 范围内的信号。 器件本身可以支持 USB3.0、因此这不是问题、 必须优化 PCB 布局以更大限度地减少反射。 布线长度可能过长、无法添加 TPD6E05U06而不会使系统不合规。 您能否提供布局? 也是不带 ESD 二极管的 VNA 波形图像。

此致、

塞巴斯蒂安

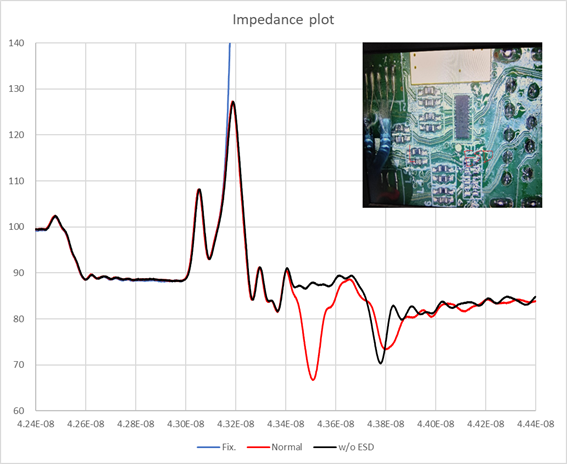

下面的阻抗图是 PCBA w ESD (红色迹线)和 不带 ESD (黑色迹线)的阻抗比较。 这表明不具有 ESD 的 PCB 布线约为90欧姆。 连接 ESD 后、阻抗下降约20欧姆。

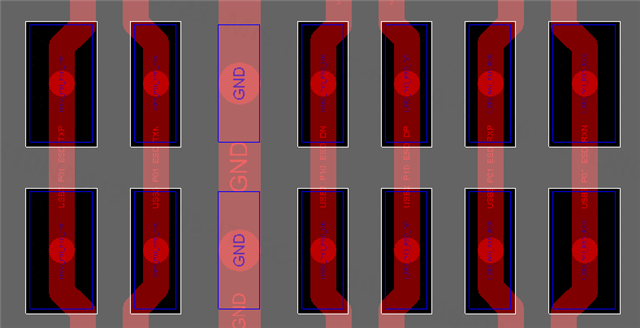

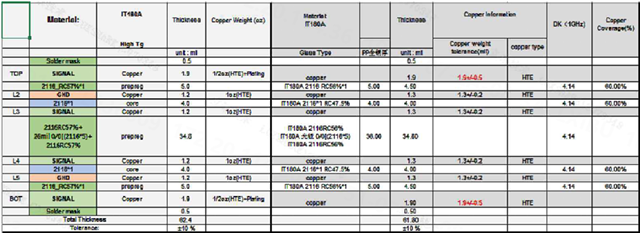

下图是 ESD 足迹及其下方的空洞。 如下面的 PCB 层叠所示、PCB 具有6层。 ESD 连接在底部。

除了优化 PCB 布局之外、客户还想了解 ESD 本身的阻抗性能。 如果 ESD 的阻抗太低、则 ESD 可以将 PCB 的高阻抗拉低。